# University of St Andrews

Full metadata for this thesis is available in St Andrews Research Repository at:

http://research-repository.st-andrews.ac.uk/

This thesis is protected by original copyright

#### ABSTRACT

## Simulation of a Paged Computer System

#### A Teaching Tool

This thesis describes the design and implementation of a simulator (written in IBM Fortran IV (Level G)) of a paged, multi-programming, single-processor, computer system.

A general justification of such a simulation is made, followed by details of the particular model chosen and implementation details.

Validation of the simulator is discussed, and followed by details of a number of experiment using various simulated job streams and configurations. Finally the response of a simulated system to two different paging algorithms is discussed and compared to known experimental data.

Finally, the use of the simulator as a teaching tool is described with details of the paging algorithm interface with the rest of the model.

# SIMULATION OF A PAGED COMPUTER SYSTEM

A TEACHING TOOL

Th 8806

I hereby declare that the conditions of the Ordinance and Regulations for the degree of Master of Science (M.Sc) at the University of St. Andrews have been fulfilled by the candidate, Linda A. Macaulay.

> Morven Wilson

I hereby declare that this thesis is a record done by myself, not accepted in any previous applications for a higher degree in the University of St. Andrews or elsewhere.

(Mrs.) Linda A. Macaulay

# ACKNOWLEDGEMENTS

I would like to take this opportunity to thank my supervisor, J. MORVEN WILSON, for the exceptional guidance and practical assistance which he has given me.

I am also grateful for the generous co-operation given by PROFESSOR A.J. COLE and the kind help lent by the computer staff in his department.

Further, I wish to thank MRS. J. BROWN for the excellent and speedy manner in which she typed this thesis.

#### OBJECT

The object of the thesis is to illustrate the development and validation of a simulation of a paged computer system with a view to that simulation being used as a teaching tool.

The teaching tool takes the form of a computer program written in FORTRAN. Its objective is to help computer science students see the effects of paging algorithms (written by themselves) on various timesharing system configurations and consequently to help them produce an effective algorithm.

#### CONTENTS

#### PART I INTRODUCTION

- Il. Introduction to Computer System Simulation

- a. What is Simulation?

- b. Why Simulation?

- c. Simulation Throughout the Generations.

- I 2. The Construction of a basic simulation model - BASYS.

#### PART II THE SIMULATOR

- II 1. Description of the system to be simulated

- a. General features of the system

- b. Basic queueing and progress of a job through the system.

- II 2. The Simulation Model

- a. Requirements

- b. Level of Detail

- c. Language Selection

- d. Representation of Jobs

- e. Structure of the Model.

#### PART III VALIDATION and EXPERIMENTATION

- III 1. Validation Methodology

- III 2. A Question of Balance

- III 3. Validation of the Model

- a. Response to different job parameters

- b. Response to different machine configurations

- c. Response to a Paging Algorithm.

- III 4. A Comparison of Two Paging Algorithms.

# PART IV THE TEACHING TOOL

# IV 1. How to use the Simulator Introduction

- a. The System Configuration

- b. The Job Stream

- c. The Interface with the Paging Algorithm

- d. Output from the Simulator.

# PART V CONCLUSIONS and FUTURE DEVELOPMENTS

PART I

INTRODUCTION

## I. 1. INTRODUCTION TO COMPUTER SYSTEM SIMULATION

#### a. WHAT IS SIMULATION?

Simulation is a technique for obtaining information about the performance of a system without actually putting that system into operation. A model of the system is constructed so that the results obtained by operating the model indicate the results to be expected when the corresponding real system is operated. The model may then be modified and operated to indicate the behaviour of the real system if it was also so changed.

Basically, the simulation technique is to create a model of the system by keeping lists of items at each stage in the process and transferring items from one list to another in the correct chronological order. The transferring of an item from one list to another usually represents a transition through some stage in a process and is accompanied by appropriate updating of a timing device.

#### b. WHY SIMULATION?

The thesis is concerned mainly with the investigation into the performance of a paged time-sharing system under a given set of conditions.

The two basic approaches that have been used for the investigation of existing time-sharing systems have utilized either analytic or simulation techniques.

In certain instances analytic techniques have proved quite satisfactory, for example, Scherr (1) was able to design a very simple model of the Project MAC system at MIT and Smith (2) was able to construct a model reflecting a paged time-sharing system. Analytic techniques, however, require a large number of simplifying approximations and assumptions whereas simulations require relatively few. This enables the simulation of more complex computer systems thus giving the method a great applicability.

In general, analytic models lack sufficient flexibility to allow a number of different systems or algorithms to be investigated without a great deal of extra effort. However as Nielsen has demonstrated in his 'Simulation of time-sharing systems' (3) simulations do exhibit the necessary degree of flexibility.

The disadvantages of simulation arise in the debugging of the simulation program and in deciding to what extent the simulation results are valid. The latter problem can be considerably eased if statistical measurements from a real system are available with which to compare the results from the simulation.

Paged computer systems are generally considered to be

too complex and non-deterministic in nature for analytical

methods of study. Thus the alternative chosen is simulation,

validated by subsequent comparison with a real system.

The first generation of computers employed relatively simple hardware configurations which could be "investigated" without the use of a simulation model. The need for simulation developed with the advent of the second generation of machines when configurations became more complex.

Simulations helped to give a general picture of overall system performance and provided an inexpensive and relatively easy way of investigating new design ideas.

Hardware performance was one of the first areas of the computer to which computer simulation techniques were applied. In 1957 W.E. Smith (4) developed a simulator for the internal logic of computer hardware components. This program was used for testing actual designs and also as a training device for designers. At a higher level, in 1964, M.S. Zucker (5) developed a simulator called LOCS (logic and control simulator) which simulated the components collectively, thus giving an overall view of the performance of the circuitry.

Simulations have been further developed to investigate the performance of the computer under various combinations of variables. One of the earlier programs of this type was published in 1964 by Statland (6) who considered such variables as equipment capabilities and I/O block sizes.

As software increased in importance it was realised that simulations were less likely to be reliable unless software and hardware-software interactions were taken into account.

Many simulations were constructed after the software system in question and were used to help evaluate proposed changes to that system, e.g. Katz (7) study of the IBM 7090/7040 Direct Coupled Operating System. Others were developed before the system in question had been built or programmed and were used in the construction of the system as well as subsequent modification, for example, IBM's 7090 time-sharing system.

with the appearance of the third generation of computer systems more comprehensive simulators were developed. For example, in 1967, Nielsen (3) published a simulation model with a general purpose design which can be used to study a variety of time-sharing systems. It can analyse performance characteristics for such varied purposes as hardware configuration, software modification and parameter adjustment, algorithm design and system development. In 1969 Seaman and Soucy (8) developed a Computer System Simulator (CSS) model package. CSS provides the user with a language and structure with which he can model a large variety of computer systems at differing levels of detail.

A recent test (9) (1970) was done on the validity of the simulation technique using the ATLAS computer at Manchester University. The operation of the ATLAS was simulated using a next-event type of simulation model and good agreement was found between the simulated results and those of the real system.

It can be seen that computer system simulations have developed hand in hand with the development of the computer, modelling proposed hardware and software architectures and configurations quickly and cheaply before any full scale commitment to their implementation. They continue to be a vital and valid tool in the investigations into the design of to-day's complex systems.

# I. 2. THE CONSTRUCTION OF A BASIC SIMULATION MODEL - BASYS

BASYS, as formulated by Macdougall (10), helps to establish the basic notions of a simulation model and to illustrate how even a simple simulator can be used to see the effects of varying certain system parameters.

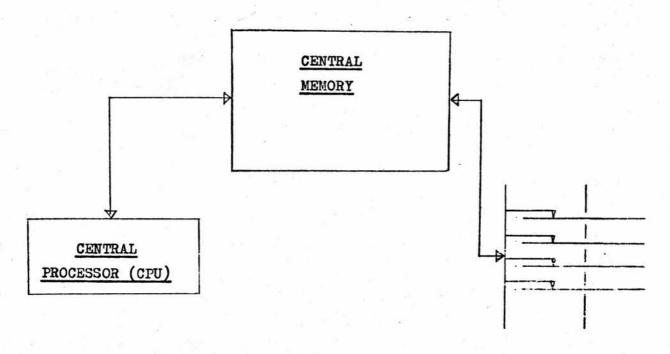

BASYS is a basic simulation model for a disk-based multiprogrammed computer system, whose configuration is shown in fig.1.

When a job arrives at the system it requests central memory space. If sufficient space is available then it is assigned to the job, otherwise the job is entered into a queue (the central memory queue) until enough space becomes available. Once it has been assigned central memory space (note that the entire program is in core) it can then begin execution. It requests the central processor. If the processor is free it is assigned to the job otherwise the job is entered in the central processor queue. When the job has been assigned the processor and starts executing it may issue I/O requests. At the point of issuing a request the job loses control of the processor and requests the use of the disk. If the disk is free it is assigned to the job otherwise the job is entered into the disk queue. Once the job has completed the I/O request it will probably require more CPU time. On regaining control of the CPU it may issue other I/O requests or continue executing until completion. On completion the job releases the processor, frees the central memory and leaves the system. Note that several jobs are in the system at the same time i.e. it is multiprogrammed.

FIG 1 HARDWARE CONFIGURATION OF BASYS

MOVABLE-HEAD DISK

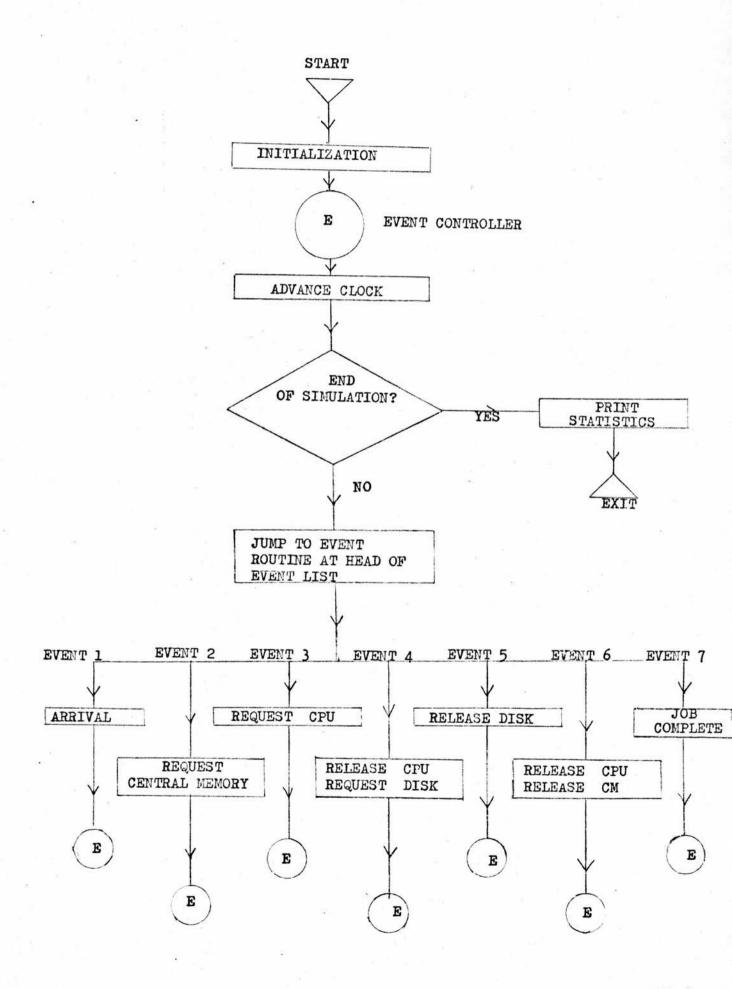

#### The simulation model

BASYS is a 'next-event' type simulator i.e. the simulated time clock is advanced to the time of the predicted next event. The events represent transition points between activities. Seven events are simulated (shown in fig.2) and four queues are dealt with, namely, the queue for central memory space, the queue for central processor attention, the queue for execution of drum transfers, and the event list. The job mix may either be read in directly by the simulator or generated within the simulator program using various known probability distributions. The flowchart of the simulator is shown in fig 2.

#### The Simulator Structure

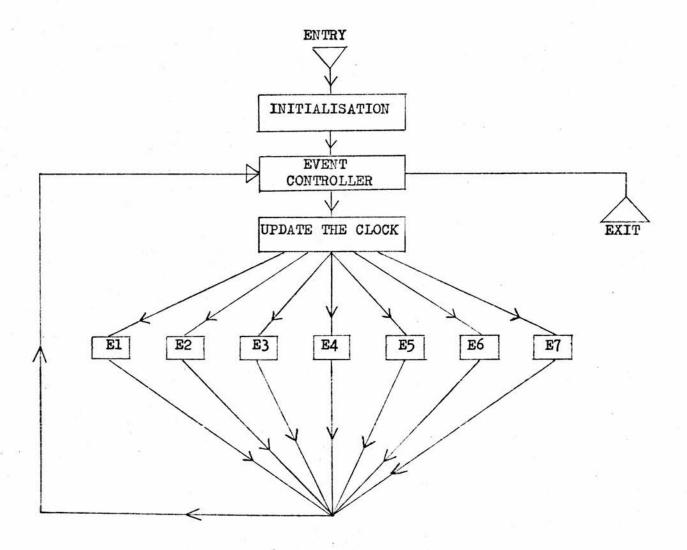

The structure of the simulator is as shown in fig. 3.

In the simulator, a job is represented by an entry in a job table. This entry contains characteristics established for the job as well as various counters for accumulating job related statistics. As the job moves through the system - enters queues, is assigned to the central processor, etc - its movement is reflected by moving a pointer to this job table entry, rather than by moving the entry itself.

The progress of the job through the system is marked by the occurrence of a series of events. Each event routine essentially does two things: it simulates the operations whose initiation corresponds to the occurrence of this event and it predicts, for the job for which the operation was performed, which event is to occur next and at what time it is to occur.

An event list facilitates the ordering of events. This is a linked list ordered with respect to the clock time at which the next event is to occur. Thus the head of the list is the job whose next event is to occur at the earliest point in simulated (clock) time. A typical snapshot of the list at some point in time might appear as follows:

CLOCK TIME = 100

| NEXT EVENT   | EVENT TIME | <u>JOB</u>        |   |

|--------------|------------|-------------------|---|

| RELEASE DISK | 101        | 20 ← HEAD OF LIST | 7 |

| REQUEST CPU  | 109        | 18                |   |

| JOB ARRIVAL  | 117        | 22                |   |

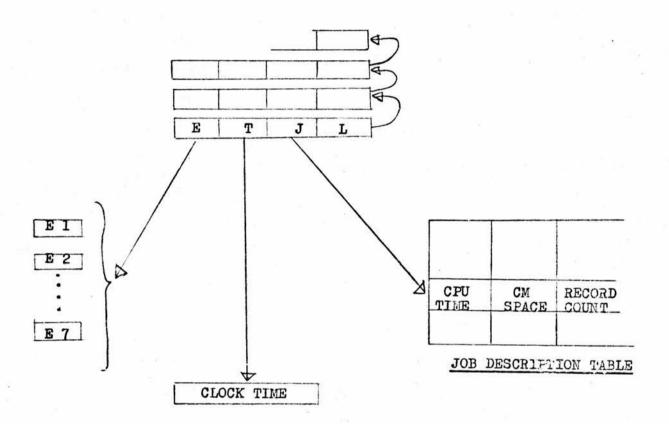

All event routines in the BASYS simulator make entries in the event list, but only one routine (the Event Controller) removes entries from this list. The structure of the event list is shown in fig. 4.

The event controller controls the occurrence of all events in the simulator and always transfers control to the event routine specified by the head of the event list. When the corresponding event has been completed and the job returned to the event list or entered into a queue, then control is always returned to the event controller.

The basic steps in the event scheduling are:

- 1) The event controller removes the entry at the head of the event list. This entry specifies an event time T, an event identifier E, and a job table pointer J.

- 2) The clock is updated to time T.

# KEY

E - EVENT IDENTIFIER

T - THE PREDICTED TIME AT WHICH EVENT E IS TO OCCUR

J - THE JOB TABLE ENTRY POINTER

L - LINK TO NEXT ENTRY IN EVENT LIST

- 3) The event controller transfers control to the event routine E.

- 4) The event routine E performs the required processing for the job, and if possible determines its next event (and inserts the event identifier E<sup>1</sup>, event time T<sup>1</sup> and a job table pointer J into the event list). If such a determination is not possible the event routine E enters the job into a queue.

- 5) Control is then returned to the event controller.

If, as is sometimes the case, the next event for the job cannot be predicted, no entry for the job can appear in the event list. This situation arises when the job has to be entered into a queue, for example, when the disk is busy or when there is a shortage of central memory space. Once the facility becomes available, and the job reaches the head of the queue, an entry is inserted into the event list to make the 'next event' a request for the facility which was previously unavailable, for example, request disk, request central memory space etc.

All queues in BASYS are represented in the form of linked lists. BASYS lends itself to a straightforward implementation in GPSS and SIMSCRIPT, and with the addition of a few elementary list processing routines can be effectively implemented in FORTRAN.

The main advantage of BASYS is that it allows for extensions and additions to the basic model. Thus it can be used as a basis for more extensive simulations of computer systems with greater complexity.

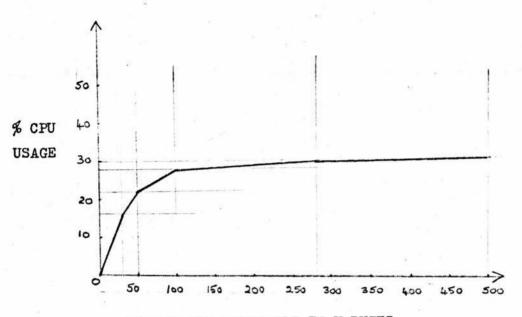

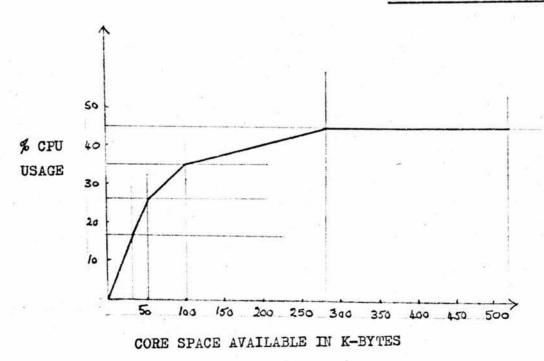

EXPERIMENTS AND RESULTS from implementation of BASYS in FORTRAN. Two main experiments were carried out. Both were to measure the utilization of the central processor in respect of

- 1) increasing the amount of central memory available

- 2) replacing the disk with a faster model

Results are shown in figs 5A and 5B.

#### CONCLUSIONS

Experiments show that after a certain point increasing the amount of core memory available has no effect on the percentage usage of the CPU. This point is reached when the total core memory requirements of all the jobs can be satisfied simultaneously. Results further show that increasing the disk speed by a factor of two gives a proportional increase in the usage of the CPU. This can be seen by comparison of the curves given in fig.5A.

The BASYS simulation model has thus shown how even a simple model can be used to investigate the effects of varying certain parameters on the simulated computer system.

From the point of view of the thesis the implementation of BASYS was an exercise to aid familiarization with the principles of a simple computer system and some basic simulation techniques. The BASYS model is still available as a teaching tool if required, but the thesis now progresses to the more challenging problem of simulating a paged multiprogramming computer system.

# GENERAL TRENDS FROM RESULTS

# ONE DISK REV. IN 25 MILLISECS

CORE SPACE AVAILABLE IN K-BYTES

# ONE DISK REV. IN 12 MILLISECS

THE MAXIMUM CORE SPACE REQUIRED BY THE 20 JOBS WAS 356 K-BYTES

| K SIZE | % CPU |  |

|--------|-------|--|

| 25     | 16    |  |

| 50     | 26    |  |

| 100    | 34    |  |

| 275    | 44    |  |

| 510    | 44    |  |

| RVTIM | = | 12 |

|-------|---|----|

| K SIZE | % CPU |

|--------|-------|

| 25     | 14    |

| 50     | 21    |

| 100    | 28    |

| 275    | 30    |

| 510    | 30    |

RVTIM = 25

RVTIM - TIME TAKE FOR ONE DRUM REVOLUTION

KSIZE - SIZE OF CORE MEMORY IN K-BYTES,  $K = 2^{10}$

% CPU - % CPU USAGE

Figure 5C

JOB DESCRIPTION OF 20 JOBS RUN THROUGH BASYS

| Job | Central Memory | CPU Time | Number of    | Mean Inter-      | Record |

|-----|----------------|----------|--------------|------------------|--------|

| No. | Space Required | Required | I/O Requests | Request Interval | Size   |

| 1   | 7520           | 50       | 10           | 5                | 360    |

| 2   | 6480           | 30       | 10           | 3                | 360    |

| 3   | 10100          | 60       | 20           | 3                | 360    |

| 4   | 15210          | 70       | . 10         | 7                | 360    |

| 5   | 6110           | 30       | 10           | 3                | 360    |

| 6   | 20360          | 100      | 20           | 5                | 360    |

| 7   | 12220          | 80       | 20           | 4                | 360    |

| 8   | 4140           | 10       | 10           | 1                | 360    |

| 9   | 17770          | 70       | 10           | 7                | 360    |

| 10  | 9080           | 30       | 10           | 3                | 360    |

| 11  | 20200          | 60       | 10           | 6                | 360    |

| 12  | 10000          | 40       | 10           | 4                | 360    |

| 13  | 12100          | 50       | 10           | 5                | 360    |

| 14  | 8800           | 30       | 10           | 3                | 360    |

| 15  | 6070           | 10       | 10           | 1                | 360    |

| 16  | 51610          | 140      | 20           | 7                | 360    |

| 17  | 72130          | 200      | 40           | 5                | 360    |

| 18  | 7120           | 30       | 10           | 3                | 360    |

| 19  | 31010          | 90       | 10           | 9                | 360    |

| 20  | 36700          | 110      | 20           | 5                | 360    |

|     |                |          |              |                  |        |

# Inter-Arrival Time of Jobs

All jobs arrived at the system at fixed equally spaced intervals.

PART II

THE SIMULATOR

#### II 1. DESCRIPTION OF THE SYSTEM TO BE SIMULATED

# a. GENERAL FEATURES OF THE SYSTEM

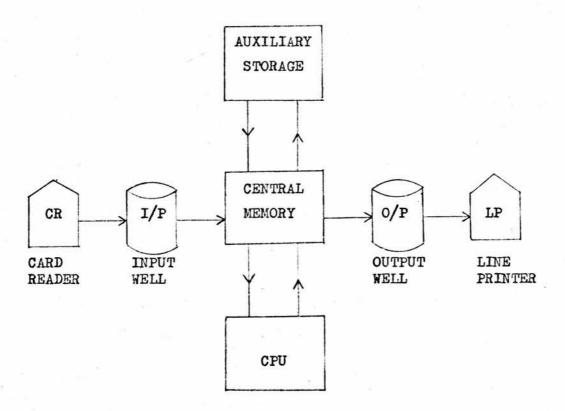

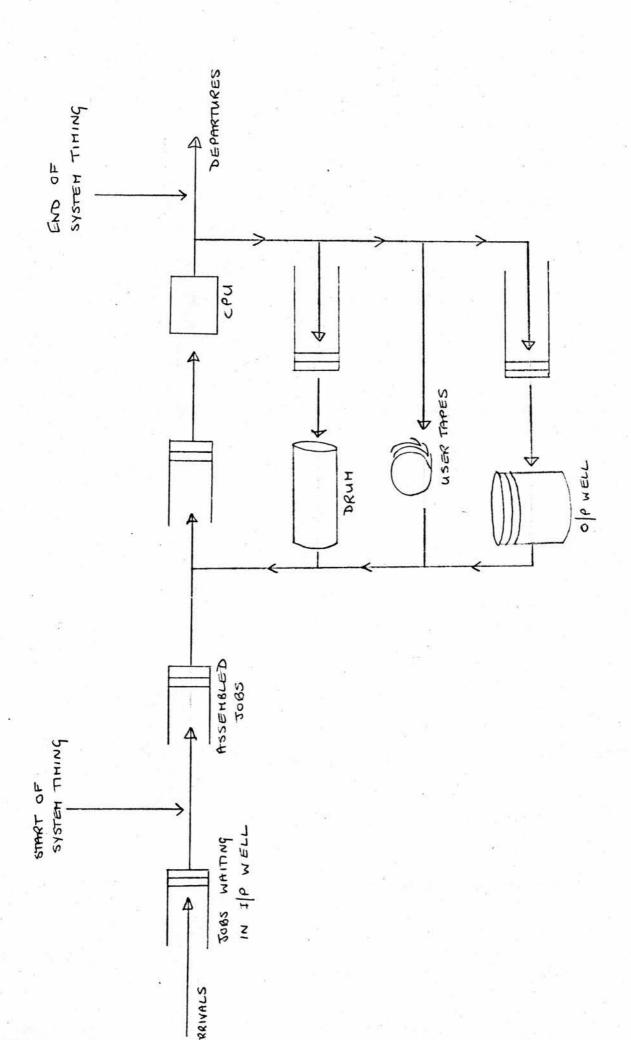

The system under investigation consists of a paging memory, paging auxiliary storage (drums) and one central processing unit. The complete configuration is shown in fig.6.

Basically, the simulator implements a time-sharing, multiprogramming system with provision for logical-to-physical address mapping by either simple paging or demand paging. It has several special features which are discussed in some detail below.

These are:- 1. Paging and demand paging

- 2. Working Set strategy

- 3. Ready List

#### 1. PAGING AND DEMAND PAGING

The object of the study is to produce a simulator which will be sensitive to changes in the paging algorithm; thus it is essential that a paging core memory and a paging drum are included in the system.

Systems which incorporate paging are troublesome from a simulation point of view (as Boote et al. remark in their simulation (9))since the page turning events take place much more frequently than program-swapping events on a non-paged computer. The real time necessary to complete a simulation is therefore longer. Scherr's simulation (1) of a non-paged IFM 7094 had a simulated-time to real-time ratio of

approximately 24, whereas Nielsen's simulation (3) of the paged IBM 360/67 on an IBM 360/50 had a ratio close to 2.

## APPROACH TO PAGING

Paging is a set of techniques whereby programs and main memory are broken into small units and the program pieces are located in corresponding sized blocks anywhere in main memory. The paging techniques incorporated in our system allow a straightforward implementation of a logical-address space larger than the physical-address space.

In our paged system, physical memory is considered to be broken up into "blocks" of a fixed size. The term "page" refers to units of logical space, while equal-sized units of physical space are called blocks. The programs are also considered to be split into "pages" of a size equal to the block size of physical memory. Thus the address is such a system is considered to be represented by two numbers:

- (1) a page address or number

- and (2) a word-within-page address.

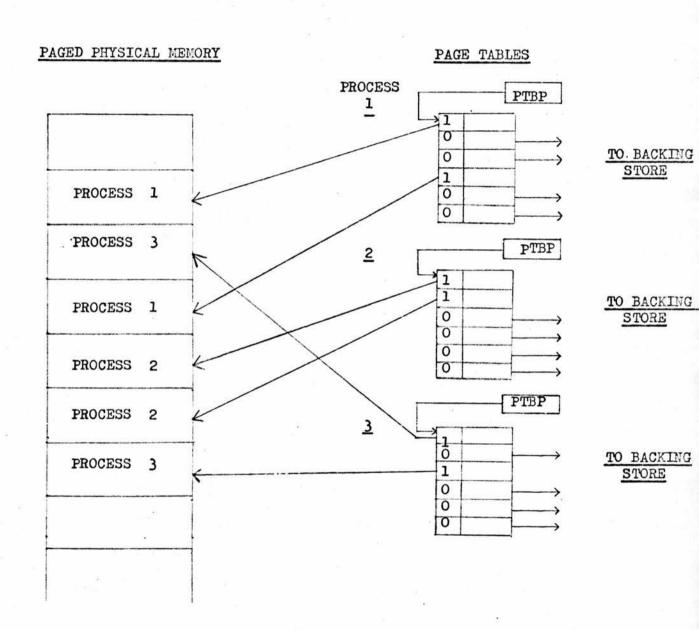

A paging mechanism requires a table, called a <u>page-table</u>, or map with one entry for each page in order to perform address translation from logical to physical space. The complete memory map used in our system is shown in fig.8 and the page table in fig.7.

One page table exists for each process. The physical-block number corresponding to a given page is found by a table look-up

#### LOGICAL ADDRESS

#### note

IF M=1 THE PAGE IS IN CORE: THUS BLOCK NO ENTRY GIVES ACTUAL PHYSICAL ADDRESS OF THE PAGE.

IF M=O THE PAGE IS NOT IN CORE:

THUS BLOCK No GIVES ADDRESS ON

AUXILIARY STORAGE. THE PAGE

MUST BE BROUGHT INTO CORE BEFORE

THE PHYSICAL ADDRESS CAN BE

CALCULATED

PTBP - PAGE TABLE BASE POINTER

in this page table using the page number as index. The control bits ("in-core" bits) in each table entry are used to indicate whether the page represented by that entry resides in memory or on an auxiliary storage device. The page number from the logical address when added to the contents of the page-table base register indicates which word in the page table contains the block number where the page resides. The figure in the block number portion of the table indicates an actual starting address for the page in main memory or a location on auxiliary storage where the page can be found. If the control bits indicate that the latter case holds, a call to the system, referred to as a page fault, is generated to fetch the page to memory before resuming computation. Using this approach, the logical-address space can be smaller, equal to, or larger than the physical-address space.

At the start of computation only a single "starter" page is loaded into main memory, not the entire process. Then as references are made to pages not currently in main memory, the page-table would indicate the fact by generating a page fault which causes the supervisor, to bring in the page. This approach is known as demand paging.

Thus paging and demand paging are incorporated in the system by means of the page table and memory map. It should be stressed, however, that no attempt has been made to introduce the segmentation concept into the system.

#### 2. THE WORKING-SET STRATEGY

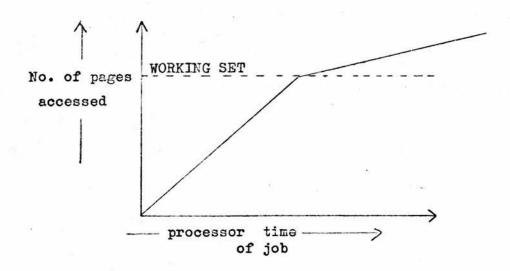

Several recent studies on the behaviour of programs in a paging environment (11,12,13,14,15) lead to the conclusion that over short periods of time instruction and operand references are confined to a subset of the set of pages comprising the logical address space, and that once this subset is established its content varies only slowly. Thus it seemed desirable to include some method by which information about the behaviour of programs could be made available to the students paging algorithm.

Denning (11) defines this subset of pages as the 'workingset'. He shows how the working set can be detected and suggests

an algorithm which makes use of this information. Our simulation

model detects the working set but the paging algorithm supplied

by the user may use or ignore the information gathered. (see

'The Simulation Model').

## Description of the Working Set

The working set of information is the smallest collection of information that must be present in main memory, at any instant, to ensure efficient execution of a program.

The operating system is responsible for determining on the basis of page reference patterns, which pages constitute the working set at any instant and for detecting those that leave the working set. In practice the operating system considers the working set of information, associated with a process, to be the set of most recently referenced pages within some arbitrary period of time.

To initiate a process on the processor a "starter page" is loaded and subsequent pages are demanded until the working set of pages is built up. When a page has not been referenced for a measured period (see later) then it leaves the working set and may be rolled out of core.

# Formal definition of the Working Set

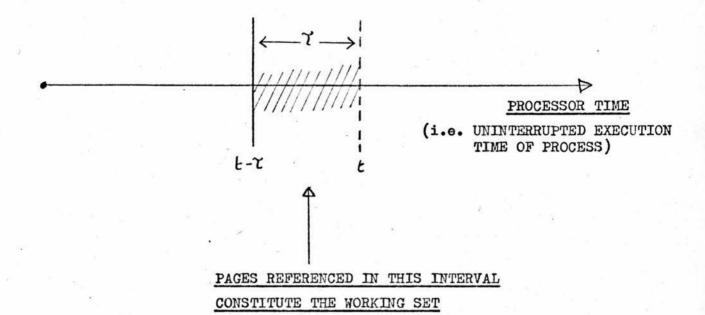

The working set W(t,7) of a process at time t is the collection of information referenced by the process during the process time interval (t-7,t).

Thus the information a process has referenced during the last  $\tau$  seconds of its execution constitutes its working set, see fig.9.

The working set consists of information referenced during the last  $\tau$  seconds; however, in our system we are usually interested in the <u>pages</u> which contain this information. Thus the pages themselves constitute our measure of the working set since the information required is only accessible in page sized blocks.

#### Properties of the Working Set

#### 1. size

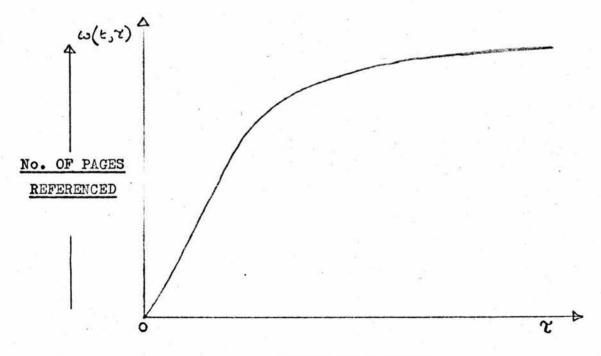

The size of the working set  $\omega(t,\tau)$  is the number of pages referenced in this interval

i.e.  $\omega(t,\tau)$  = number of pages in  $W(t,\tau)$ .

On consideration of the working set size it is obvious that in an interval of zero length, no pages will have been referenced. It is further clear that in longer intervals of time more pages will be referenced. Thus the general curve suggested by  $\omega$  (t, $^{\chi}$ )

is monotonically increasing as shown in fig.10. (See (11) for further details)

#### 2. prediction

We would expect intuitively that the immediate past page reference behaviour of a program constitutes a good prediction of its immediate future page reference behaviour. That is to say, that for small time separations  $\infty$ , the set W(t,7) is a good predictor for the set W(t+4,7).

To see this more clearly, suppose  $<<^{\sim}$ .

Then  $W(t+\alpha, \gamma) = W(t, \gamma-\alpha) U W(t+\alpha, \alpha)$ . Since references to the same page tend to cluster in time, the probability

Pr ( W(t+x,x)  $\cap$  W(t,\cap{7}) ) tends to be small.

Therefore some pages of  $W(t, \mathcal{T})$  will still be in use after time t i.e. pages in  $W(t+\mathcal{A}, \mathcal{A})$ , since also

$$W(t, \Upsilon - \alpha) \subseteq W(t, \Upsilon) \cap W(t+\alpha, \Upsilon)$$

$W(t,\tau)$  is a good predictor for  $W(t+x,\tau)$ .

On the other hand, for large time separations  $\langle (say \langle \cdot \rangle) \rangle$ r) control will have passed through a great many program modules during the interval  $(t,t+\alpha)$ , and  $W(t,\tau)$  is not a good predictor for  $W(t+\alpha,\tau)$ .

# 3.7 -sensitivity and re-entry rate

It can be seen from fig.10, that as  $\gamma$  is reduced,  $\omega$  (t, $\gamma$ ) decreases. If the number of pages in W(t, $\gamma$ ) decreases, the probability that there are useful pages still in W(t, $\gamma$ ) also decreases. Consequently the rate at which pages are recalled to W(t, $\gamma$ ) increases. This means that if  $\gamma$  is decreased then the re-entry rate of pages will increase.

FIG 10 VARIATION OF  $\omega(t, \gamma)$  WITH CHANGES IN  $\gamma$

LENGTH OF INTERVAL

The value ultimately selected for  $\Upsilon$  will thus be of great importance to the effectiveness of using the working set strategy. Should  $\Upsilon$  be too small, pages may be removed from main memory while still useful, resulting in a high traffic of returning pages. Should  $\Upsilon$  be too large, pages may remain in main memory long after they were last referenced, resulting in wasted memory. Thus  $\Upsilon$  must be carefully chosen to strike a balance between excess page traffic and too much wasted memory.

In the system which we are simulating, a page is not rolled out of main memory immediately it leaves the working set. Instead it is 'marked' as a candidate for removal from core and will only be removed if the space it occupies has been demanded by a page of some other process. (Should the paging algorithm so decide). Note however that in the case of a read-only page (where a valid copy already exists on backing store) the page is still marked as a candidate for removal. Thus the space it occupies may be taken over by some other process in the usual way, however the page is not rolled out to backing store. The page table entries and other relevant information about the page is simply updated.

#### Detection of the Working Set

Detection procedures similar to those suggested by

Denning (11) are implemented in the system. As detailed above,

each process has a related page table which provides a map from

the logical address space to the physical address space of each

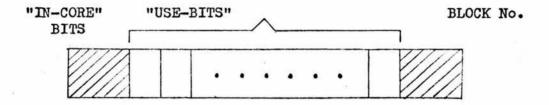

page belonging to that process. Along with the 'in-core' bits

and the 'block number' entry there is a further entry which

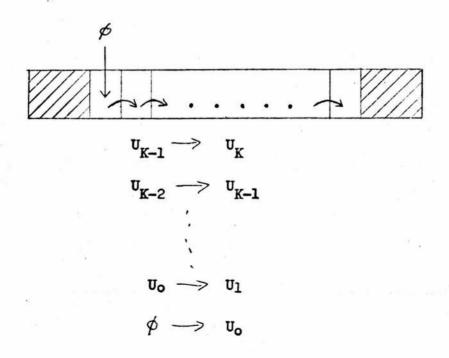

contains a string of 'use-bits'  $U_0$ ,  $U_1$ , ...,  $U_K$  (see fig.11)

The sampling interval  $\sigma$  is defined to be  $\frac{\tau}{K}$  where K is an integer constant chosen to make the sampling intervals as 'fine grain' as desired. On the basis of page references during each of the last K sampling intervals, the working set W(t,Ko) can be determined.

Each time a page reference occurs,  $U_0$  is set to 1 (whether 0 or 1 already). At the end of each sampling interval of the bit pattern contained in  $U_0$ ,  $U_1$  ...,  $U_K$  is shifted one position to the right, a 0 enters  $U_0$ , and  $U_K$  is discarded: see fig.12.

The logical sum U of the use-bits is computed:

$$v = v_0 \cup v_1 \cup v_2 \dots \cup v_K$$

so that U = 1 if and only if the page has been referenced during the last K sampling intervals. Of all the pages associated with a process, those with U = 1 constitute the working set  $W(t, K\sigma)$ . If U = 0 and M = 1 (i.e. the page is in core), then the page is no longer in the working set and is marked as a candidate for removal from main memory.

(K IS THE NO. OF SAMPLING INTERVALS)

# FIG 12 SHIFT AT END OF SAMPLING INTERVAL

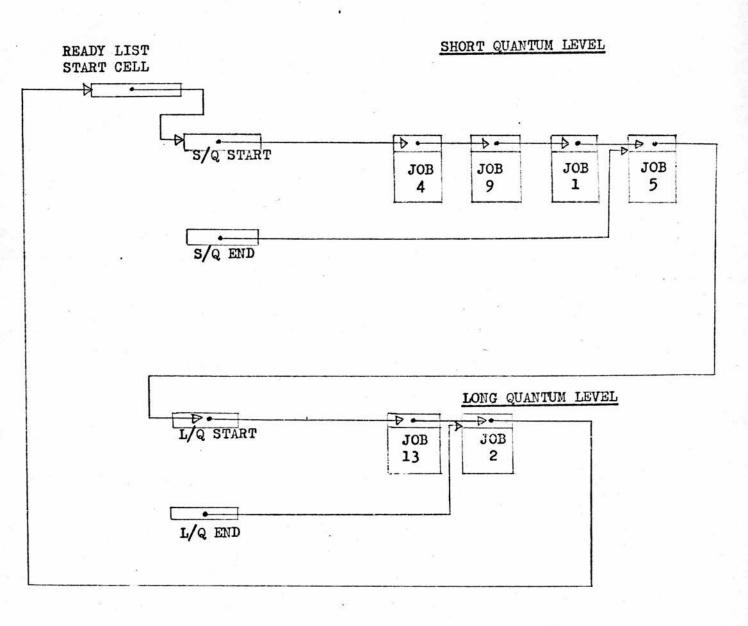

# 3. The Ready List

The Ready List is a list of processes ready to run on the central processor when it becomes available.

The Ready List has two quantum levels, a short quantum level (SQL) and a long quantum level (LQL) (see fig.13). A process is always allowed to run for a short quantum, and if at the end of this time no other process is ready to run, it can continue. The purpose of the short quantum is to assure that some useful computation takes place, in order to justify the expense of swapping the process in. This scheme also allows higher priority processes to pre-empt the processor if they appear on the SQL during or after a short quantum. When a process is dismissed after a short quantum or because a higher priority process has become ready, it is placed on the short-quantum level.

Each time a process completes a short quantum, a number, called the <u>long quantum count</u> is decremented. Once this count is reduced to zero the process is moved to the lowest-priority level, the long quantum level.

This method ensures that all processes will run with a reasonable response to each and it limits the number of times a process can appear on the high-priority level of the ready list.

#### PRE-EMPTION

A higher priority job may arrive on the ready list while a lower priority job has control of the processor. At that point pre-emption occurs and the pre-empted job is returned to

the short quantum level of the ready list. However this pre-empted job is not assigned a fresh short quantum but on regaining control of the processor will complete the remainder of its previously assigned quantum.

# I/O REQUESTS

A similar situation arises when an executing job issues an I/O request. A record is kept of the time quantum still to be completed when the I/O request is issued. The job is placed on the SQL of the ready list until the request is serviced and the job reaches the head of the list. On regaining control of the processor the job does not begin a fresh quantum but completes the remainder of its previously assigned quantum.

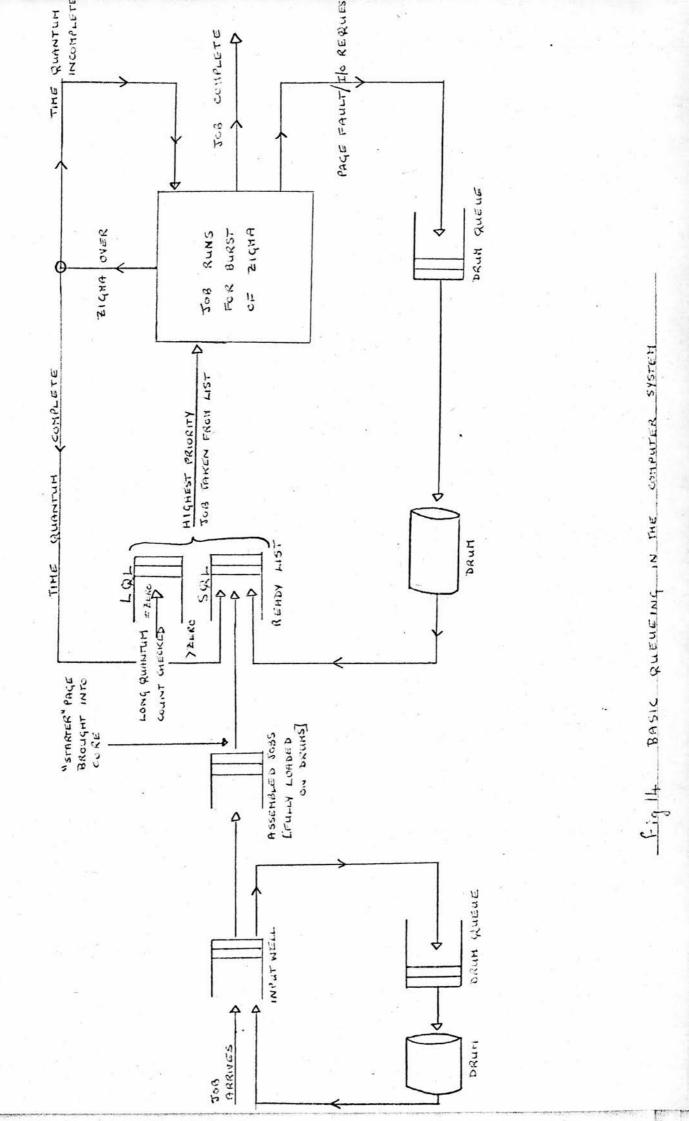

# b. BASIC QUEUEING AND PROGRESS OF A JOB THROUGH THE SYSTEM

The basic queueing incorporated in the system is illustrated in fig.14.

When a job arrives at the system it is assigned a priority and proceeds to be loaded page by page onto auxiliary storage from the input device. Compiling, assembling and linkage editing phases are ignored for simplicity in our model. Unit record I/O (e.g. card reader, line printer) are assumed to have little system overhead and to be spooled in any case.

If there is enough room in core for the job's working set of pages (see Ch. on "the Simulation Model" for an explanation of how this is decided) then a 'starter' page is loaded into core and the job is ready to begin execution.

The number of blocks necessary to contain the job's working set are reserved. This is a basic requirement of the working set strategy, since it insures that there will be enough space in core for the working sets of all jobs currently in the execution phase. Thus no job need demand blocks previously assigned to a page of another job's working set, thus minimising page traffic.

Thus a 'starter' page is loaded and the job is ready for execution. The job is placed on the short quantum level of the ready list. When it reaches the head of the list the central processor is assigned to the job and begins execution.

The job executes until one of four possible events arise.

- 1. it issues an I/O request

- 2. it references a page not in core, i.e. a page fault occurs

- 3. it completes the time quantum allocated

- 4. the job completes

In all four cases the job loses control of the processor to the job now at the head of the ready list.

In cases 1 and 2 the job enters the queue for drum attention. In case 1 the required I/O processing takes place and the job is returned to the ready list. In case 2 the paging algorithm is consulted and makes the decision as to which block of physical memory is to be allocated to the page being brought into core. Once the page is in core the job is returned to the ready list.

When the job completes the time quantum allocated (case 3) the long quantum count for that job is decreased by one. If this count is positive the job is placed back onto the short quantum level queue; if it is zero or below then the job is placed on the long quantum level queue. If there are no other jobs on the ready list the job is simply allowed to continue processing for a further quantum.

If the job completes it relinquishes all core memory space and auxiliary storage space, all related tables are cleared and all references to the job in the system are removed, and appropriate statistics compiled.

# II 2. THE SIMULATION MODEL

#### a. REQUIREMENTS

In order to allow the user to observe the effect of paging algorithms which he may have written for this reasonably complex time-sharing system, the model had to fulfil three requirements.

First, the model was to serve as a test vehicle for very diverse paging algorithms. It had, therefore, to be responsive to changes in these routines. Further, the paging algorithm had to be relatively isolated from the rest of the model so that changes could readily be programmed and incorporated. An efficient interface had to be developed.

Second, the model had to be responsive to changes in the configuration of the system, for example, to changes in core size, drum size and drum speed. Such changes would help determine the efficiency of the paging algorithm under differing conditions. Further, the configuration had to be easily adjustable, such as by appropriate modification of parameter values.

Third, the model was to serve as a means of determining the effect of various job mixs and loads upon the performance of the paging algorithm, the performance of the system and throughput of jobs. Thus it had to be responsive to adjustments in the requirements of particular jobs. Further, the job stream had to be easily adjustable, such as by the change of a few parameters.

# b. LEVEL OF DETAIL

Since the paging algorithm was to be of such great importance the model had to keep track of every page in the system at all times. The identity and current state of jobs had to be retained over time slices, I/O waits and page fault waits.

Care had to be taken not to include disproportionately scaled activities in the model, since this would lead to an inefficient model, for example, all I/O for user programs is assumed spooled onto the drum. Activities, such as delays due to dynamic address relocation, the effects of associative memory operation, compilation, linkage editing were ignored. Compilation and linkage editing are assumed to be merely the processor and I/O operations of another job, (i.e. the compiler and the linkage editor). Those activities with a level of detail finer than the activities at the paging level were not included. Similarly, activities with a level of detail more gross than those at the paging level were excluded. Thus, for example, the amounts of drum storage space required for job's pages are to be specified as parameter values, and the presumption is made that enough blocks will be available on drums. A simple pencil and paper calculation will enable the user to ensure that this is so.

Consequently, the basic unit of time was chosen to be 100 psec and of storage to be the page, the size of the page being a variable parameter.

When including information about the working set in the paging algorithm, results will be affected by the values of the

sampling interval,  $\sigma$ , and the number of sampling intervals, . Thus at the level of detail catered for here, it was decided to include  $\sigma$  and  $\kappa$  as variable parameters.

## c. LANGUAGE SELECTION

Since this simulation model is to be used as a teaching tool, it is important that the program implementing the model should be readily understood. Thus it was decided to write the program in a language that is commonly known and which has a high degree of portability. FORTRAN appeared the best choice to fit the requirements.

Since the program is a simulation, it might normally be expected that it be written in a simulation language. However these languages generally have a poor execution speed relative to general purpose languages and often utilize memory space rather inefficiently. Speed and efficient memory utilization were relevant to the simulation since it has to be within the range of time and space allowed to students' everyday jobs. Although simulation languages have built-in queueing facilities, these can be easily implemented in FORTRAN subroutines. Further FORTRAN enables a closer approximation to the actual workings of the system than would be possible using the simulation languages generally available to computer users, since different types of queuing techniques may be used at different points throughout the model. The queuing techniques may be readily created to satisfy the particular requirements of this model.

## d. REPRESENTATION OF JOBS

As with many simulation models (e.g. Nielsen (3),(16) and simulations used for design purposes) we are dealing here with a model of a computer system which does not yet exist.

Consequently there is the immediate disadvantage of not knowing exactly what the job mix will be and how the jobs will behave during execution.

Nielsen's simulation of time-sharing systems acts as a simulator both for existing time-sharing systems and for the design of such systems. Thus the job mix will vary from system to system and in some cases may be entirely unknown. He has developed a job description language in which eight instruction types are used to indicate the desired behaviour of a job during its simulated execution. Description sequences for a particular job are constructed from a set of master sequences which represent a prototype for each different job type.

Katz's (17) simulation for System /360 machines used a Job Generator. Frequency distributions and tables of information giving the overall statistical properties of the user's job population were used as input to the Job Generator. The latter was designed so that the set of jobs produced reflected the actual jobs of a particular user's installation.

In a simulation study of the optimization of performance of time-sharing systems (18) the job-stream is generated using Monte-Carlo techniques. This method was adopted in an attempt to reduce the number of parameters required to describe the job mix.

The approach used in our simulation model is based on characteristic equations for the paging behaviour of jobs and random number generators and frequency distributions for other aspects of the jobs' behaviour. All the information used is based on results of various studies on the behaviour of programs in a paging environment (18, 12, 13, 14, 15).

Following is a description of how this simulation handles the job-description parameters and the justifications for the methods chosen.

# prediction of I/O requests

I.F. Freiberg, in a paper entitled 'Dynamic Behaviour of Programs' (15) presents results obtained from an instruction by instruction interpretive execution of different classes of programs on an IBM 7044. He claims that the data obtained can be used as realistic input to simulation models of multiprogrammed and fixed page size computer systems. Part of the data showed that most of the supervisor calls occurred for I/O operations and further that a program does not execute very many instructions between successive supervisor calls. From this it was concluded that it would be desirable to include the time taken between successive I/O requests as a parameter for individual jobs. It appears that the value of this parameter should generally be small relative to the total execution time of a job. Being a parameter however it may be varied from job to job so as to make some jobs virtually I/O bound and others relatively free from I/O activity.

The actual parameter of the interarrival time of successive I/O requests is expressed in terms of a maximum i.e. the parameter represents the maximum interval between successive requests. The time between individual requests is generated by means of a random number generator which generates values between 1 and the parameter specified.

prediction of page faults

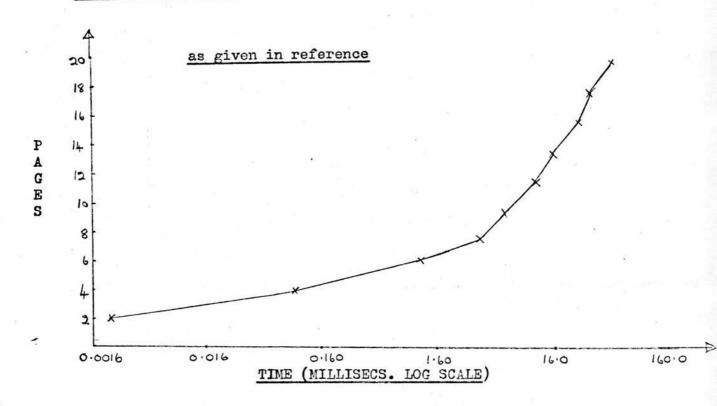

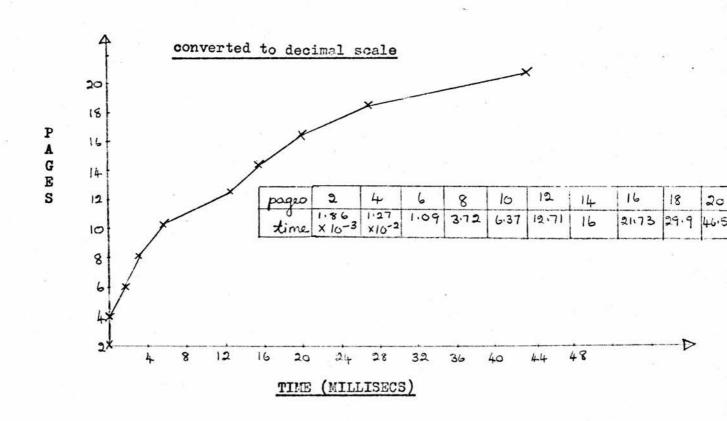

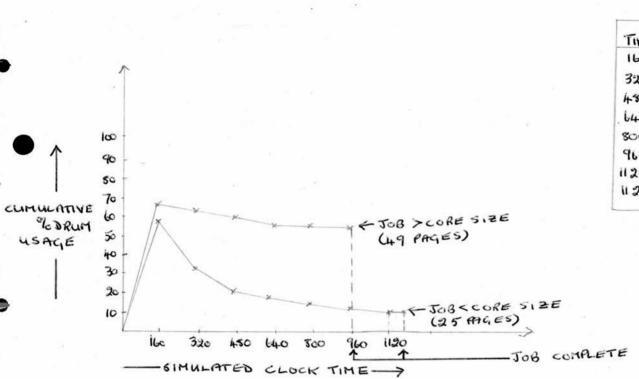

Fine, Jackson and McIsaac (12) did an empirical study in which programs were executed in an interpretive manner on an AN/FSQ-32 computer. Their results illustrate, among other things, a page demand as a function of time as shown in fig.15.

The number of pages accessed initially is extremely high. On average, the first 10 pages were required in less than 5.6 ms; in half of the cases, these first 10 pages were required in less than .8 ms. In this paper five rather large programs were studied, namely LISP, 44 pages; META5, 14 pages; GPDS, 41 pages; TINT, 23 pages; SURE, 30 pages. The page size was taken to be 1k words. The programs were not in any way designed for a paged machine. Even with the difference in the functions of the programs considered, the over-all pattern of page demands was shown to be fairly consistent.

The conclusions of the study express three basic points:

- In general programs demand pages at very rapid rates until they have 'sufficient' pages in core.

- 2. Frequently programs do not run for very long even after having acquired a sufficiency of pages.

FIG 15 PAGE DEMAND

DYNAMIC PROGRAM BEHAVIOR UNDER PAGING, FINE et al (See Ref. 12)

3. For those programs which do run for a time after acquiring a sufficient number of pages, this number is usually a considerable proportion of the total number of pages associated with the program.

In an empirical interpretive study of programs on the IBM 360/50 computer, Varian and Coffman, in 1967, produced similar results concerning page faulting activities. In 1968 they published a further study which included an experiment in which they varied the number of pages of a job allowed to remain in core during execution. This concluded that programs operating with substantially less than half their pages in core caused excessive page turning.

The studies of Freiberg and Varian and Coffman show that once a process begins execution, the page-access characteristic tends to that given in fig.15. They further agree with Fine et al in the evidence that excessive page turning takes place when programs are made to operate while substantially less than core-resident. This implies that the subset of information necessary for efficient execution of a program must be relatively large. Consequently the 'working-set' of pages (as defined earlier) must consist of a large proportion of the program's total pages.

Thus it was decided to develop equations which would predict the page fault rates using the empirical evidence discussed so far. It was seen to be desirable to have different

equations for differing points in the job's execution. The curve in fig.15 was thus approximated by two straight lines whose point of intersection was taken to be the point where the working set had been reached, see fig.16. Note, however, that we are concerned only with the <u>number</u> of pages in the working set and not their individual identity.

Since demand paging is operable in this system it is possible that the paging algorithm will permit active pages of one process to be removed from core to make room for those of another process which is currently in control of the central processor.

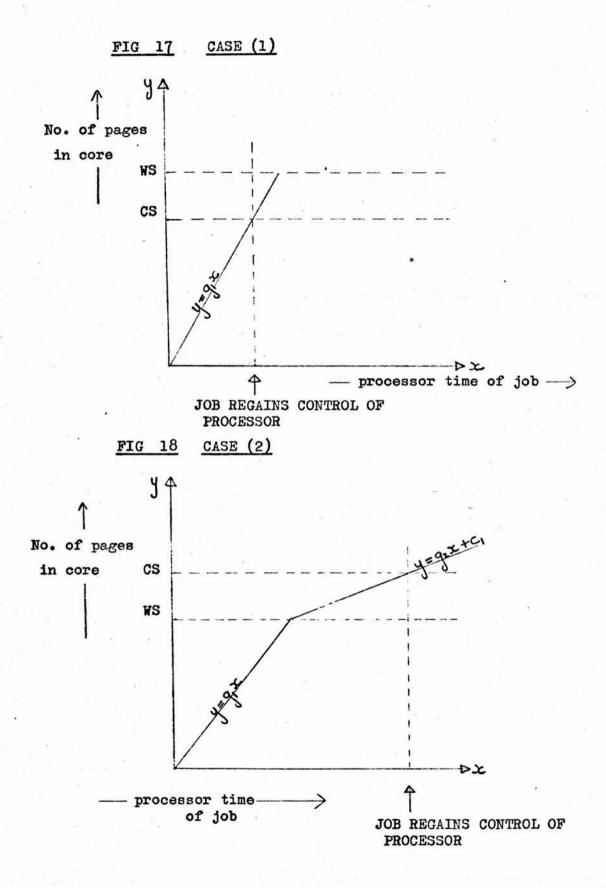

In the simulation model the equations are such that at any point in time they can always predict when the next page fault is going to occur for a particular process. The rate of the page faulting for that process will be affected by the number of its active pages which have been removed since it last had control of the processor. Thus the rate of page faulting of a process at any point in time can be any of the five possible conditions following:

let the current set of pages in core = CS

let the working set of pages for the process = WS \*

let the number of active pages removed = NPR

<sup>\*</sup> as discussed on P31 the working set size should be a large proportion of the process's pages. We fix this proportion at \( \frac{2}{3} \) rds. (Though this may be altered)

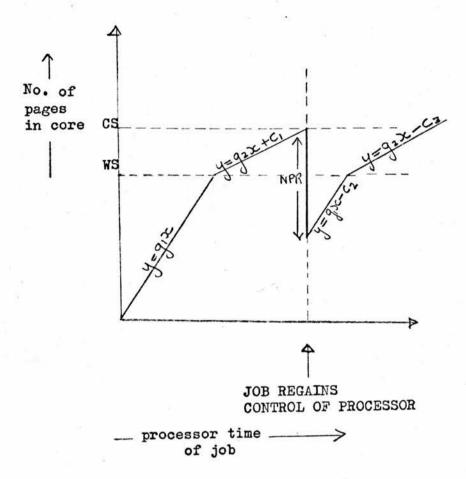

- (1) CS WS-1 and NPR = 0 (fig.17)

- (2) CS WS-1 and NPR = 0 (fig.18)

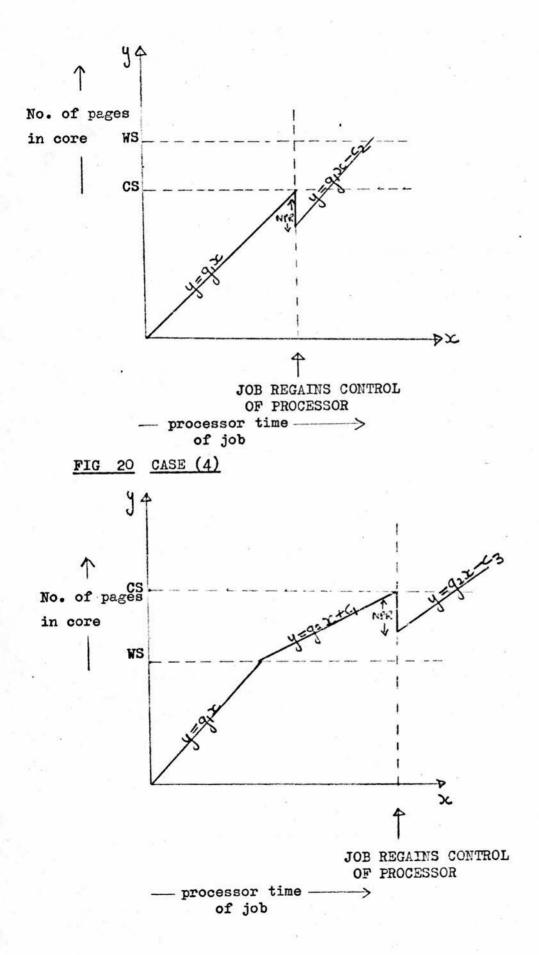

- (3) CS WS-1 and NPR 0 (fig.19)

- (4) CS WS-1 and NPR (CS-WS) (fig.20)

- (5) CS WS-1 and NPR (CS-WS) (fig.21)

The point in time that is of most interest is that point at which the process regains control of the processor, since the equations must be able to predict when the next page fault is going to occur.

The actual rates at which the page faults are to occur are given by the slopes of the lines, i.e.  $g_1$  before the working set is in core and  $g_2$  after the working set has become core-resident. The values of  $g_1$  and  $g_2$  will be parameters of a particular process, as is the value for WS, thus enabling different job types to be assembled.

The values of the constants c<sub>1</sub>, c<sub>2</sub>, c<sub>3</sub>in the equations are found by simple geometric and arithmetic calculations.

details of the equations

# Case (1) CS < WS-1 and NPR = 0 see fig.17

On regaining control of the central processor the current set of pages is less than the working set and no active pages have been removed. Thus the process continues to issue page faults at the initial rate for that process i.e.  $y = g_1 x$ .

Consequently if the process regains control at some point (PROTIM) in the uninterrupted processor time of the job and that job currently has CS pages in core, the next page fault will occur at  $x = (CS+1)/g_1$ .

# Case (2) CS ≥ WS-1 and NPR = 0 see fig.18

In this case the current set of pages in core is greater than the working set. No active pages have been removed and the page-demand rate continues at the second rate i.e. according to  $y = g_2x + c_1$  where  $c_1 = WS(1 - g_2/g_1)$  ( $c_1$  is calculated from the fact that the lines  $y = g_2x + c_1$  and  $y = g_1x + c_2x + c_3x + c$

Thus if the process regains control at PROTIM the next page fault will occur at  $((CS+1) - c_1)/g_2$ .

# Case (3) CS < WS-1 and NPR > 0 see fig.19

The current set of pages is less than the working set but some active pages have been removed. Thus the process will continue to issue page faults at the first rate i.e. according to  $g_1$ , until the working set number of pages are in core. There is however a displacement from  $y = g_1x$  to consider, thus the page fault rate will be according to  $y = g_1x - c_2$ . (see fig.22 for calculation of  $c_2$ ) If the job regains control of the processor at PROTIM then  $c_2 = g_1$  x PROTIM + NPR - CS and the next page fault will occur at  $x = (CS - NPR+1+c_2)/g_1$ .

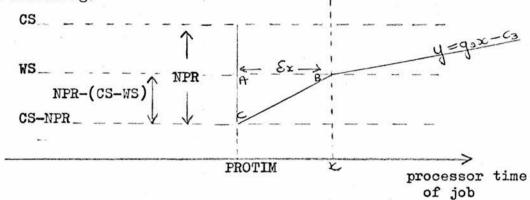

# Case (4) CS > WS-1 and NPR < (CS-WS) see fig.20

The job regains control at a point (PROTIM) where the number of pages in core is greater than the working set of pages, some active pages have been removed but these do not interfere with the working set. Thus the rate of page faulting will now follow the line given by  $y = g_2x - c_3$  i.e. will be at the second rate.  $c_3 = g_2$  (PROTIM +  $\frac{NPR - (CS-WS)}{g_1}$ ) - WS see fig. 22 for calculation. The next page fault will occur at  $x = (CS-NPR + c_3)/g_2$ .

# FIG 19 CASE (3)

# Case (5) CS > WS-1 and NPR > (CS-WS) see fig.21

The job lost control of the processor when the number of pages in core was greater than the number in the working set. On regaining control the job finds that so many of its active pages have been removed that there has been interference with the working set. Thus the job now page-faults at the initial rate  $g_1$  until the working set is restored i.e. along the line  $y = g_1x - c_2$  where  $c_2 = g_1$  x PROTIM + NPR - CS.

Thus if the job regains control at PROTIM the next page fault will occur at  $x = (CS-NPR + 1 + c_2)/g_1$ .

# Other aspects of job description

So far we have discussed the methods by which the model handles prediction of I/O requests and page faults. The remaining job description variables are:

Priority

Core size requirements

Long quantum count (for working set strategy)

CPU time required

Record size of job.

These may be specified by any method the user of the model requires. The subroutine which generates pseudo-random numbers is made available to the user at the time of specification. Further details about job parameter specification may be obtained in Part IV Ch 1, pages 70 -77.

# FIG 22 CALCULATION OF C2, C3

It is clear from fig.21 that the lines  $y=g_1x-c_2$  and  $y=g_2x-c_3$  intersect at y = WS, x unknown. A closer look at fig.21 shows the following:

In the triangle ABC, les  $\delta x$  be the unknown side AB then x = PROTIM +  $\delta x$

from the diagram:

the gradient of

$$CB = \frac{AC}{AB}$$

i.e.

$$g_1 = \frac{NPR - (CS - WS)}{\delta x}$$

thus

$$\delta \approx = \frac{NPR - (CS - WS)}{g_1}$$

Thus the lines

$$y = g_1x-c_2$$

,  $y = g_2x-c_3$  intersect at  $y = WS$ ,  $x = PROTIM + NPR - (CS-WS)$

to find

$$c_2c_3$$

$$y = g_1x-c_2$$

$$y = g_1 (PROTIM + NPR - (CS-WS)) - c_2$$

$$g_1$$

$$c_2 = g_1xPROTIM + NPR-CS$$

$$y = g_1x - c_3$$

$$WS = g_2 (PROTIM + NPR - (CS-WS)) - c_3$$

$$g_1$$

$$c_3 = g_2 (PROTIM + NPR - (CS-WS)) - WS$$

# e. STRUCTURE OF THE MODEL

The model is similar to that used for BASYS since it is a next event type simulation model and simulates seven events. The events contain considerably more detail and are more closely interrelated than in BASYS but the basic structure is the same as fig.3. see fig.23

These seven events are ordered by means of an event controller which is basically a linked list ordering events with respect to the time at which they are due to occur. Each event simulates some process which a job may go through whilst in the computer system and predicts when the next event for that job will occur. It is sometimes necessary for a job to enter a queue e.g. awaiting central memory space, awaiting use of the drum to complete an I/O transfer or to wait on the ready list. The event list does not contain an entry for a job while it is in a queue but once the job reaches the head of the queue it is removed from that queue and placed on the event list.

The events which are simulated are described below:

Event 1 Simulation of Job Arrival

The event 1 routine samples the job mix distributions for job N for which the event is taking place. It has the following functions:-

- 1. determines maximum interarrival times of I/O requests for the job N

- 2. determines the page fault rates  $g_1$ ,  $g_2$  for the job N

4923 THE SIMULATOR STRUCTURE

- 3. assigns a priority to the job

- 4. generates the central memory requirements for the job

- 5. generates a long quantum count associated with the job

- 6. predicts the approximate central processor time required by the job

- 7. predicts the approximate size of the working set of pages for that job

- 8. generates the record size for the job.

The routine then calculates the number of pages in the job (this will vary according to the current page size in the system), and determines the size of the working set (for prediction of page faults). Event 2 is then scheduled for job N and the arrival time of job N + 1 is predicted. Event 1 is scheduled for job N + 1 and control is returned to the event controller.

An event is "scheduled" by linking up the associated job entry on the event list. That is, the event number and the time at which the event is due to occur are entered into the event list along with the job number with which they are associated. The event then occurs when this entry reaches the head of the event list i.e. when it is the first event in time due to occur. When this entry reaches the head of the list the time associated with the event is closest to the

time on the simulation clock. The simulation clock is then advanced to the time associated with this event.

The clock is initially set to time zero at the start of the simulation and is advanced only when an event takes place. The clock allows for several events to occur at the same time since it is only advanced when the time associated with an event is greater than that of the clock. The time at which an event is "scheduled" to occur is always greater than or equal to the clock time.

# Event 2 Page Loaded onto Drum

The Event 2 Routine simulates the loading of a page of job N onto the drum from an external device. If the drum is busy then the request is entered into a drum queue. If the drum is free it is assigned to job N for a time that is a function of the drum speed, read/write rate, number of records associated with job N and traverse time. If, however, all the pages of job N have been loaded onto the drum then job N is assigned to the queue for central memory space and event 7 the internal scheduler is scheduled for it. If pages are still being loaded event 3 routine is scheduled, representing the delay time in completing the loading of a page.

#### Event 3 Completion of Loading

Event 3 represents the completion of the loading of a page. The drum is freed and the entry at the head of the drum queue for job H is examined. If it was in the drum queue to

to load another page onto the drum then event 2 is scheduled for job H. However if it was in the queue to carry out an I/O transfer or deal with a page fault then event 4 is scheduled for job H.

Job N has completed the loading of a page so the page table for job N is updated to keep account of the position on the drum that the page is stored. The list of free pages available on the drum is also updated. Event 2 is scheduled for job N.

## Event 4 Drum Request

The Event 4 routine simulates the use of the drum for I/O transfers and page faults. If the drum is busy job N is entered into a queue otherwise the drum is assigned to job N and event 5 is scheduled.

### Event 5 Drum Completion

Event 5 signifies the completion of a drum transfer for I/O or a page fault for job N. Job N is then placed on the Ready List since it is once more ready to run on the CPD and event 7 is scheduled for this job. The drum is now free and if there is anything in the drum queue then the head of the queue is assigned to the drum and event 2 or event 4 scheduled as appropriate for job H.

### Event 6 CPU Execution

The event 6 routine simulates the actual running of a job on the central processor.

The processor is reserved and pointers set up indicating

which job has control of the processor (CPUJOB) and what time it gained control (CPUST). The job now in control of the processor continues executing as if it had never lost control and all its counters and associated statistics are continued and updated. Firstly, if the job has completed a multiple of  $\sigma$  (zigma) (the sampling interval) units of time in execution then the use-bits of the job are shifted one place to the right.

A) Secondly, if the job has completed its estimated CPU time then event 7 is scheduled for the job and control returned to the event controller.

Thirdly, if an I/O request has not already been predicted to occur at a certain time then one is predicted and a flag set up to say that this I/O request is waiting to be carried out. Similarly if a page fault has not already been predicted then one is predicted and a further flag set up to say that this page fault has still to be satisfied.

A test is done to see whether the I/O request or the page fault is to occur first. Suppose it is the page fault then a further test is done to see if this page fault is to occur within the next burst of zigma on the CPU. If it is then event 7 is scheduled to deal with the page fault and control is returned to the event controller. Similarly with the I/O request.

If neither the page fault nor the I/O request is to occur within the current burst of zigma then the job completes zigma.

The use-bits are shifted and the whole process (from A) above) is repeated provided the job still has some of its time quantum left. If the job has completed the time quantum allocated to it then event 7 is scheduled where the job will be put onto the ready list. Control is then returned to the event controller.

# Event 7 Internal Scheduler

The Event 7 is a simulated combination of a high level and low-level scheduler. This routine selects the next "suitable" job to put onto the ready list and also decides which job is to run next on the CPU. Thus it replenishes the ready list and keeps the CPU busy.

Assume Event 7 has been called to deal with job N.

If job N is in the central memory queue then all its pages have been loaded onto drums and it is now requesting that its first ("starter") page be loaded into core so that it might begin execution. Suppose the working set strategy is being adopted, then the "starter" page is loaded into core provided that there is enough room for its working set (the size of which has been predicted in the event 1 routine). The working set number of pages are reserved out of those available in core. Thus event 7 initiates the loading of the "starter" page into core, event 4 is scheduled for job N and control returns to the event controller. If the scheduler decides not to load the initial page then control is simply returned to the event controller.

If job N is not in the central memory queue and it is on the ready list then it is requesting use of the CPU. If the CPU is free then it is assigned to job N and job N removed from the ready list. Event 6 is scheduled and control is returned to the event controller.

If, however, the CPU is not free then the scheduler must test if the priority of job N is greater than that of CPUJOB (i.e. the job currently in control of the CPU). If its priority is greater then pre-emption occurs, job N is removed from the ready list and is scheduled for event 6. CPUJOB releases the CPU and the appropriate statistics are updated.

If CPUJOB is complete all its table references are deleted and blocks occupied by it on the drum and in core are freed. The central memory queue may now be advanced if it is possible (same argument as earlier).

If CPUJOB is not complete then in the current implementation a random bit pattern is put into the "use-bits" to simulate the page reference patterns during its last run on the processor (the bit pattern is put into "working set" number of pages only, the random numbers lying between 1 and 2<sup>K</sup> where K is the number of sampling intervals). The pages which have been written to or updated during the last run on the processor are also generated randomly and their page tables updated accordingly. The pre-empted job CPUJOB is then placed on the ready list and control returned to the event controller.

If, however, the priority of job N is not greater than CPUJOB but the CPU is still busy then job N is placed on the ready list, and control returned to the event controller.

Suppose now that job N has just been executing on the CPU and has been blocked for some reason.

If the job is complete all references to the job are deleted and the sequence of instructions carried out as when CPUJOB completed (see earlier).

If the job is not complete "use-bits" are updated, pages

"written-to" are indicated and page tables updated as before.

Now the reason for blocking must be determined.

If the job has blocked for an I/O request to be carried out, related statistics are updated, the CPU is released and event 4 scheduled for job N.

B) If K sampling intervals of processing have been completed by job N, each page in job N is tested to see if it is still in the working set (i.e. logical sum of "use-bits" equals 1 when the page is in core). If it is found that the page is no longer in the working set then it is marked as a candidate for removal from main memory, as an aid to the paging algorithm. Then the scheduler selects the head H of the ready list to run next. If its quantum has run out then it is assigned a further quantum according to the level of the ready list from which it is taken. If it is taken from the short quantum level, it is assigned a short quantum and its long quantum count is decreased by one. Event 6 is scheduled for job H and control is returned to the event controller.

If the job N has not blocked for an I/O request it may have blocked for a page fault. If so related statistics are updated and the CPU is released. The paging algorithm is consulted to determine which block in core is to be allocated for the demanded page. Related statistics are updated and event 4 is scheduled for job N. The sequence of decisions are then the same as if it had blocked for an I/O request (i.e. from B) ) and the head of the ready list is run next.

A further possibility is that the job has blocked because it has completed the time quantum allocated to it. In this case the long quantum count is decreased by one and the job returned to the appropriate level of the ready list. If there is no other job on the ready list this job continues with control of the CPU, otherwise the head of the ready list is selected to run next.

PART III

VALIDATION AND EXPERIMENTATION

## III 1. VALIDATION OF THE MODEL

## INTRODUCTION

The question posed in this chapter is:

Is the model a valid representation of the type of system

we are trying to model?

In some ways this is a philosophical question and a problem common to all modeling and simulation experiments. There are several accepted approaches to this problem discussed in (19,20). The approach employed here assumes that the model is valid if it satisfies the following three conditions:

- (1) That the logical and mathematical relations employed in the frame-work of the model closely approximate those in the system.

- (2) That the input parameters and variables compare favourably with known historical data.

- (3) That the simulation model's predictions of the behaviour of the real system correspond closely with that actually observed.

#### INVESTIGATION

The model under consideration was built to simulate paged, multiprogramming computer systems. It is impossible to prove the validity of the model for all such systems. However, we choose one typical machine for which known historical data is

available. Further, for the machine we have chosen empirical output data is also available with which to compare the results from the simulation model.

By experimentation with a model of this particular system we can see whether or not the three conditions are satisfied.

If they are then we have made some progress towards proving that this is a valid model.

No attempt is made to provide conclusive evidence of the validity of the model; however, the experiment to follow and the general trends indicated in subsequent chapters should provide strong indications that the model does fulfil its purpose.

## METHOD

The system chosen for comparison is the ATLAS computer once located at Manchester University since statistics are available concerning its operation in (9,21).

We first consider condition (1).

A brief description of the ATLAS system is given here and indications of how the logical and mathematical relations in the system are approximated by the model.

The basic queueing in the system is shown in fig.24 and by comparison with fig.14 can be seen to have the same basic structure as that of the system represented by our model.

However, the model does not cater for user tapes and a discussion on the approximations used follows later.

SYSTEH BASIC QUEUEING IN THE ATLAS COMPUTER

Once jobs leave the input well they are assembled according to a priority scheme which tries to maintain a tape job and a non-tape job in the execution phase at the same time. This is implemented in the model. Jobs queue to enter into the execution phase and the number of jobs simultaneously in the execution phase is limited to two. In our model jobs queue on the ready list to await execution and the number of jobs simultaneously in the execution phase is variable according to the length of the ready list. Thus, we set this at two.

In the execution phase pages are transferred to or from the drum, tape transfers may be made to one or more magnetic tapes assigned to a job, and output may be created on the output well located on disk. In the simulator transfer of pages and creation of output information all takes place as if on drums with appropriate timing considerations. This does not have a detrimental effect on the balance of the model of the ATLAS operations since no queueing takes place for transfers to or from user tapes, (each tape is connected to core via a separate channel).

The queue discipline for drum transfers and for the use of the output well is first-in-first-out. In the queue for CPU attention, however, tape jobs are given priority over non-tape jobs. These queue disciplines are mirrored in the simulation model.

Thus the logical structures in ATLAS are reflected in the model without any major adjustments.

The mathematical relations in the system are mainly represented by the parameters given for ATLAS, including

core size = 32 pages of information

mean tape transfer time = 0.062 secs/page

mean drum transfer time = 0.014 secs/page

drum size = 133 pages

supervisor overhead to transfer control to a job = 0.002 secs supervisor overhead to locate a page on the drum = 0.006 secs

The paging algorithm is described as a "one level store learning program" which is based on information held in "use digits". For each page of core store there is a use digit which is set when the page is accessed. All the use digits are scanned and reset at regular intervals by the central executive and a pattern of use is established. The selection of the page to be rolled out of core is made with respect to this pattern of use. This learning program is very similar to the one described in our original system. The "use-bits" in the original system being the "use digits" described here. Thus to give the paging algorithm in our model the degree of efficiency experienced by the one in ATLAS, the selection of the page for removal from core is based on the condition of the use-bits. Further, the page whose use-bits are furthest to the right will be the one selected. This is effectively a Least Recently Used paging algorithm.

Thus the logical and mathematical relations employed in the frame-work of the model closely approximate those in the system and condition (1) is therefore satisfied.

We now consider condition (2). Here a set of input parameters is described. These are based on historical data given in (9).

The parameters together with variables described earlier are used as input to the model, the final proof of the validity of the model lies in the results obtained as output. These are discussed later, (see page 506)

#### input parameters

class 2 is considered from (9), with compute time range 1-8.

#### class 2

maximum processor requirements = 8 secs

maximum byte requirements 208000 (page size 4K)

mean no. of tape transfers mean no. of I/O requests

max. inter I/O request interval = 8/344 secs for tape jobs  $0.23 \times 10^{-1}$  secs

page size = 4K

The input parameters actually used in the simulation are as follows:

#### GENERAL

- a) core size = KSIZE = 32 pages = 128K in subroutine SYSTEM

- b) page size = KPAGE = 4K in subroutine SYSTEM

- c) 2 levels of priority were given to jobs to account for tape jobs and non-tape jobs:

IF

$$(PJ.EQ. (PJ/2) *2) JOBDES(PJ,1) = 1$$

in subroutine JOBSIM

d) traverse time for drum transfers

TRAVT = mean tape transfer time + mean drum transfer time

= 0.038 secs

$\simeq 4$  time units (1 time units =  $\frac{1}{100}$  sec)

in subroutine SYSTEM

e) NJOB = 2 in subroutine JOBSIM so that not more than two jobs may be in the execution phase at the same time.

The supervisor overheads mentioned earlier are considered small enough to be neglected and the drum size of the system is maintained at its maximum value (KSIZE = 744) since there will thus be sufficient pages for both tape and non-tape jobs.

## FOR CLASS 2 JOBS

- f) maximum processor requirements = 8 secs

MAXCPU = 800 time units

- g) maximum byte requirements = 208000 MAXBYT = 208000

- h) maximum inter I/O request interval = 0.023 secs IOMAX (PJ) = 2 time units

The Least Recently Used paging algorithm was used in both cases. NEWLIM was set to 10000.

#### RESULTS

### Comparison of Observations from ATLAS and Results from Simulator

| ATLAS |                             | Simulator                                       |  |  |

|-------|-----------------------------|-------------------------------------------------|--|--|

| mean  | compute time<br>=380 units  | estimated CPU time of 2 jobs =269 and 564 units |  |  |

| mean  | elapsed time<br>=3770 units | response time of 2 jobs = 1879 and 4313 units   |  |  |

#### CONCLUSION

The results obtained show that the simulation model's predictions of the behaviour of the real system correspond closely with that actually observed. Thus, the model satisfies condition (3) and proves that the simulator is capable of modelling a particular system.

## III 2. A QUESTION OF BALANCE

Our model has been shown to be valid for a particular system configuration, but we require it to be valid for all systems with the properties of the system described in Part II Ch.1.

Care has been taken to ensure that the frame-work of the model reflects the logic of such systems. The user of the model, however, is responsible for the choice of input variables and parameters describing the system. His choice of system must be made carefully since it will have considerable effect on the performance of the model and consequently on the predicted performance of his chosen system.

It is possible that the user may choose "unreasonable" input parameters which will result in an unbalanced computer system. Such an unbalanced system may produce distorted simulated results and could render the system and consequently the model completely insensitive to a change in paging algorithm.

In this section, we propose some simple tests, inspired by J.H. Saltzer (22) which will help the user determine whether or not he is working with a balanced system.

The balance problem we shall consider is whether or not the core memory and processor are balanced relative to each other and to the presented job load.

#### THRASHING

Before meaningful conclusions can be drawn about system balance it is necessary to convince ourselves that balance

measurements are not distorted by "thrashing", that is, excessive overhead caused by quantum runout or page swapping.

Consider first the case of QUANTUM RUNOUT. This concerns the values of the two parameters QANTUM (1) and QANTUM (2) which upperbound the amounts of continuous processor time allocated to a job when it leaves the short quantum and long quantum levels of the Ready List respectively. These quanta of CPU time may be given values which are too small, in which case the prime cause of processor switching will be quantum runout rather than the job blocking itself.

In addition to causing extra overheads in the system, excessive processor switching may also reduce the average response times of jobs in the system. For an intuitive notion why this is true, consider 10 jobs each of which need 5 secs of processor time. If each is to run to completion, followed by the next, the first job will be served after 5 secs, the second after 10 etc... and the last after 50 secs. On the other hand, suppose that each job is served for only 1 sec, then the processor is switched to the next, etc. in a round robin. In this case, the first job to enter the system will not leave until 46 secs have passed, the last still leaving at 50. (Since processor switching causes some overheads delay times would probably be even greater).

It is difficult to decide conclusively that processorthrashing is being caused by quantum runout but a reliable guideline may be obtained through a comparison of the response time of jobs to their respective CPU requirements. If their response times are very great compared with their CPU requirements then it is likely that processor-thrashing has occurred and that the parameters QANTUM (1) and QANTUM (2) need adjusting to increase the processor time quanta allocated to the jobs.

Consider next, thrashing caused by excessive PAGE SWAPPING.

This situation arises when pages of a job are being rolled out of core before the job has finished with them. That is, pages of other jobs are demanding core space and are getting it at the expense of removing pages which are still in use (i.e. still in some job's working set). In such circumstances pages are rolled out of core only to be rolled in again almost immediately upon a page fault.

Excessive page swapping has three possible causes

- 1) the paging algorithm

- 2) the size of core

- 3) the size of jobs in the system

The paging algorithm determines which block of core and under what conditions that block of core is to be allocated to a "demanded" page. Its decision-making policy could cause a page to be removed from core when still in use. Thus a page may be rolled out of core only to be referenced again almost immediately necessitating another page replacement decision and further roll-out/roll-in hence core thrashing will occur.

The number of pages of memory available may be insufficient for the total number of job pages in the system.

When the competition for physical memory becomes very high due to over commitment vigorous page-swapping will take place i.e. thrashing will occur. Hence either the size of core or number and hence total storage demand of active jobs in the system must be altered.

Thus if thrashing caused by excessive page swapping is detected then alteration to one or more of the above three factors may be necessary.