# University of St Andrews

Full metadata for this thesis is available in St Andrews Research Repository at: <u>http://research-repository.st-andrews.ac.uk/</u>

This thesis is protected by original copyright

## APPLICATIONS OF MICROPROCESSOR TO INTERFACING TECHNOLOGY (SCSI)

## **Elizabeth Ann McKinnon**

1011

<sup>a</sup>s a té

The Als

## Declaration for the Degree of M.Sc.

I, Elizabeth Ann McKinnon hereby certify that this thesis has been composed by myself, that it is a record of my own work, and that it has not been accepted in partial or complete fulfilment of any other degree or professional qualification.

Signed:

Date: 4.10.88

## ABSTRACT

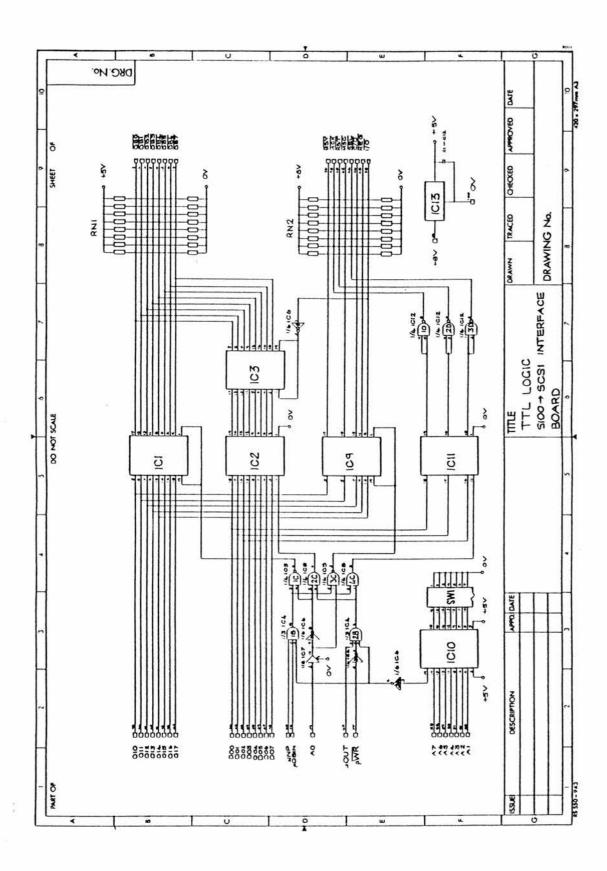

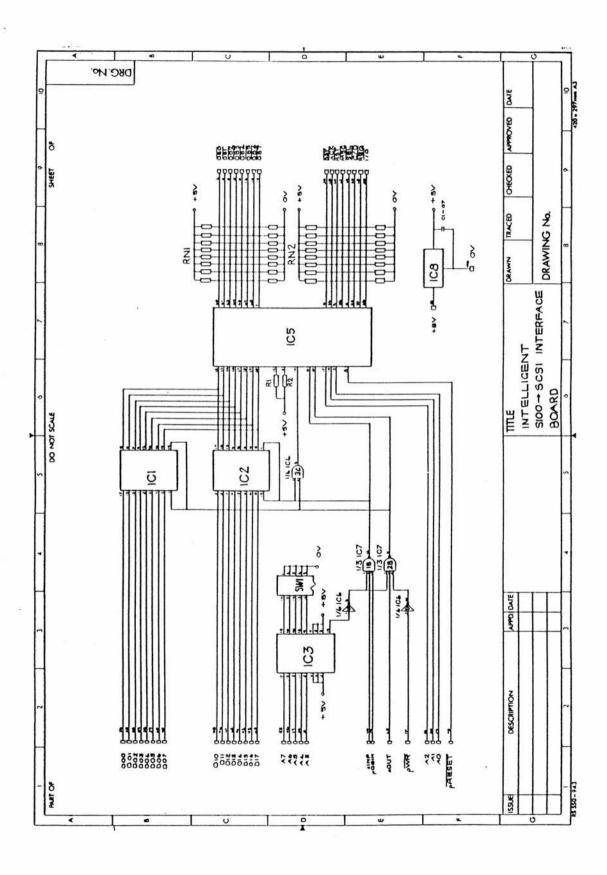

A study of the S-100 interface and the Small Computer System Interface (SCSI) was carried out. An interface board was built to communicate between the S-100 interface and a hard disk drive supporting SCSI. Two methods of communication were investigated. The first interface board used only standard TTL logic and the second interface board used TTL logic and a VLSI SCSI controller (NCR53C80).

## ACKNOWLEDGEMENTS

I would like to acknowledge the support and guidance given to me by Dr Reg C G Killean throughout this project.

I would like to thank Professor Wilson Sibbett and the University of St Andrews for giving me the opportunity to undertake a Master of Science degree.

I would also like to thank the everyone in the department who gave me access to the computers and printers necessary to compile and print this thesis.

## CONTENTS

- 1 CHAPTER 1:S-100 BUS ARCHITECTURE

- 2 Power Supply

- 3 Address Bus

- 3 Data Bus

- 3 Clock And Control Signals

## 6 CHAPTER 2:CROMEMCO SINGLE CARD COMPUTER

- 7 Power Supply

- 8 Clocks

- 8 Z80A CPU

- 11 System Reset

- 12 SCC Memory

- 13 SCC Input/Output Ports

- 19 SCC Interrupts

- 19 SCC Timers

- 20 UART Configuration

#### 25 CHAPTER 3: THE SMALL COMPUTER SYSTEM INTERFACE (SCSI)

- 27 Hardware

- 29 SCSI Bus Phases

- 36 SCSI Bus Conditions

- 37 SCSI Commands

## 42 CHAPTER 4:ADVANTAGES OF SMALL COMPUTER SYSTEM INTERFACE42 Advantages For Hard Disks

## 44 CHAPTER 5:TTL LOGIC INTERFACE BOARD

- 44 Input/Output Buffers

- 46 Input/Output Buffer Enabling

- 47 General Components

- 47 Selecting The Input/Output Buffers

- 50 Control Signals

- 51 Bus Phases

- 55 Software

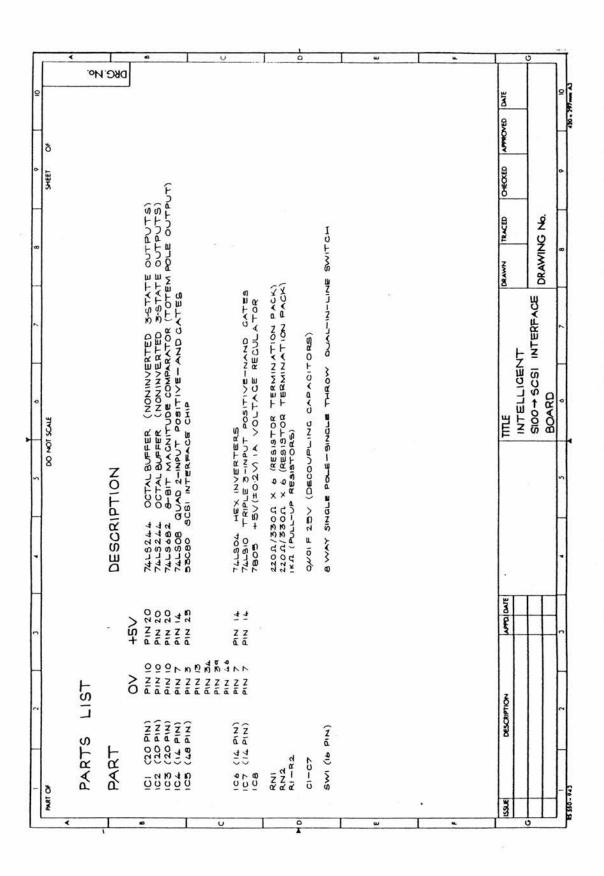

#### 59 CHAPTER 6:INTELLIGENT INTERFACE BOARD

- 59 Input/Output

- 62 Input/Output Selection

- 63 General Components

- 64 Selecting The Input/Output

- 65 Control Signals

- 66 NCR53C80 Internal Registers

- 70 Bus Phases

- 76 Software

## 79 CHAPTER 7: USES OF THE SCSI SYSTEM

79 Example Functions

## A1 APPENDIX A:TTL LOGIC INTERFACE BOARD SOFTWARE A2 MAIN.Z80

A12 EQU.Z80

A13 MSG.Z80

A14 VDU.Z80

A17 SCSI.Z80

## B1 APPENDIX B:INTELLIGENT INTERFACE BOARD SOFTWARE B2 NCR.Z80

## C1 APPENDIX C:BUS PHASE SEQUENCES

## D1 APPENDIX D:COMPARISON OF PERFORMANCE OF TTL BOARD AND NCR 53C80 BOARD

## CHAPTER 1

## S-100 BUS ARCHITECTURE

The industry standard S-100 bus was originally designed at Stanford University for use with the Intel 8080 microprocessor. As a result, the bus signal definitions closely follow those of the 8080 system. The S-100 bus physically consists of 100 parallel lines (50 on each side of the connector), either etched onto a printed circuit board or, in its origination, hard wired. The printed circuit board with the S-100 edge connectors on it is referred to as a "motherboard". Table 1.1 shows the S-100 bus signals.

## Table 1.1 : S-100 Bus Signals

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | +8V<br>+18V<br>XRDY<br>VI0<br>VI1<br>VI2<br>VI3<br>VI4<br>VI5<br>VI6<br>VI7<br>NMI<br>DMA3<br>A18<br>A16<br>A17<br>SDSB | 26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43 | pHLDA<br>A5<br>A4<br>A3<br>A15<br>A12<br>A9<br>DO1/DATA1<br>DO0/DATA0<br>A10<br>DO4/DATA4<br>DO5/DATA5<br>DO6/DATA6<br>DI2/DATA10<br>DI3/DATA11<br>DI7/DATA15<br>A11 | 51<br>52<br>53<br>54<br>55<br>56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68 | +8V<br>-18V<br>DMA0<br>DMA1<br>DMA2<br>sXTRQ<br>A19<br>SIXTN<br>A20<br>A21<br>A22<br>A23<br>MREQ<br>RFSH | 76<br>77<br>78<br>79<br>80<br>81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93 | pSYNC<br>pWR<br>pDBIN<br>A0<br>A1<br>A2<br>A6<br>A7<br>A8<br>A13<br>A14<br>A11<br>DO2/DATA2<br>DO3/DATA3<br>DO7/DATA7<br>DI4/DATA12<br>DI5/DATA13<br>DI6/DATA14<br>D11/DATA0 |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16<br>17                                                                                        | A16                                                                                                                     | 41<br>42                                                                                                 | DI2/DATA10                                                                                                                                                           | 66<br>67                                                                                                 | RFSH                                                                                                     | 91<br>92                                                                                                 | DI4/DATA12<br>DI5/DATA13                                                                                                                                                     |

| 18<br>19<br>20<br>21<br>22<br>23<br>24                                                          | CDSB<br>ADSB<br>DODSB                                                                                                   | 43<br>44<br>45<br>46<br>47<br>48<br>49                                                                   | DI7/DATA15<br>sM1<br>sOUT<br>sINP<br>sMEMR<br>sHLTA<br>CLOCK                                                                                                         | 68<br>69<br>70<br>71<br>72<br>73<br>74                                                                   | MWRT<br><br>pRDY<br>pINT<br>pHOLD                                                                        | 93<br>94<br>95<br>96<br>97<br>98<br>99                                                                   | DI6/DATA14<br>DI1/DATA9<br>DI0/DATA8<br>sINTA<br>sWO<br>ERROR<br>POC                                                                                                         |

| 25                                                                                              | ф<br>                                                                                                                   | 50                                                                                                       | GND                                                                                                                                                                  | 75                                                                                                       | PRESET                                                                                                   | 100                                                                                                      | GND                                                                                                                                                                          |

The signals in Table 1.1 which have a bar across them, (ie. SIGNAL), are negative logic and are asserted/active when they are 0V or deasserted/inactive when they are +5V. Signals with no bar, (ie. SIGNAL), are positive logic and are asserted/active when they are +5V or deasserted/inactive when they are 0V.

The S-100 bus allows interaction between a device operating as a bus master and a device operating as a bus slave. Briefly, the bus master, (whether temporary or permanent), initiates all bus cycles, the result of which may be to transfer data to and from the addressed bus slave. The bus slave monitors all bus cycles and, if addressed, will input or output data as required.

Signals not implemented on the S-100 bus using the Cromemco Single Card Computer (SCC) are:

| SIXTN and sXTRQ | These signals control 16 bit data transfer. |  |

|-----------------|---------------------------------------------|--|

| Sixin and Sxing | These signals control to on data transfer.  |  |

- DMA0-DMA3 These signal are Direct Memory Access control signals which arbitrate between simultaneous requests, by temporary bus masters, for control of the bus.

- VI0-VI7 These are the eight Vectored Interrupt lines, which control the eight levels of interrupt request priority.

- ERROR This signal is used to indicate an error during the current bus cycle. On the Cromemco SCC S-100 bus this is used to indicate speed of operation. See Table 2.1 and chapter 2.2.

A brief description of the SCC implemented S-100 bus signals follows, they are also discussed fully in subsequent chapters. The signals present on the S-100 bus can be grouped into categories:

Power supply lines Address bus Data bus Clock and control signals

## **1.1 POWER SUPPLY**

Unregulated DC power supply voltages (+8 Volts, +18 Volts, -18 Volts and Ground) are supplied from a central power supply and must be regulated on each individual board.

This method of supply has certain advantages over a single, centrally regulated supply. Firstly, every card is individually protected from voltage overload, secondly, any heat produced by voltage regulation is thermally distributed through a larger area and finally, the expansion of a computer system by the addition of cards is made easier, as voltage drop through loading of the power supply is no longer critical.

One disadvantage is that there is a danger of short circuiting the supply lines, (pins 1, 2, 51 and 52), together if a card is inadvertently moved while the voltage is on.

## **1.2 ADDRESS BUS**

The S-100 bus address lines are used to select specific memory locations or specific input/output devices. There are two types of addressing, standard addressing using A0-A15 and extended addressing using A0-A23. The Cromemco Single Card Computer uses standard addressing.

|            | Memory Locations         | Input/Output Devices |

|------------|--------------------------|----------------------|

| Standard   | Up to 65,536 bytes       | Up to 256 Devices    |

| Addressing | (64 Kbytes) Using A0-A15 | Using A0-A7          |

| Extended   | Up to 16,777,216 bytes   | Up to 65,536 Devices |

| Addressing | (16 MBytes) Using A0-A23 | Using A0-A15         |

## **1.3 DATA BUS**

There are 16 lines used for data transfer on the S-100 bus. These can be two unidirectional, 8 bit, data buses (DO0-DO7 and DI0-DI7) or one bidirectional, 16 bit, data bus (DATA0-DATA15). The Cromemco Single Card Computer board uses the two, 8 bit bus type.

## **1.4 CLOCK AND CONTROL SIGNALS**

## **CLOCK SIGNALS**

There are two clock signals present on the S-100 bus system:

- $\phi$ , (4MHz) This is the system clock, which is generated by the permanent master, and controls the timing for all the bus cycles.

- CLOCK, (2MHz) The CLOCK line is not synchronous with any other bus signal and can be used by counters, timers etc.

## CONTROL SIGNALS

The status signals identify the current bus cycle:

| <b>s</b> MEMR | Memory read           |

|---------------|-----------------------|

| sM1           | Op-code fetch         |

| sINP          | Input                 |

| SOUT          | Output                |

| sWO           | Write cycle           |

| sINTA         | Interrupt acknowledge |

| sHLTA         | Halt acknowledge      |

The control output signals determine the movement and timing of data during bus cycles:

| pSYNC | Start of new bus cycle                       |

|-------|----------------------------------------------|

| pDBIN | Gate data onto data bus                      |

| pWR   | Write from data bus                          |

| pHLDA | Data and address bus in high impedance state |

The following signals are used primarily with the Z80A microprocessor:

| pINT and NMI | Interrupt lines used to request servicing from the permanent bus master.                                                                           |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| pHOLD        | This signal is used to request control of the bus from a permanent bus master.                                                                     |

| MREQ         | This is a control signal which indicates that the address bus holds<br>a valid address for a memory read/write operation.                          |

| RFSH         | This is a control signal which indicates that the lower seven bits<br>of the address bus can be used as a refresh address for dynamic<br>memories. |

The following signals are primarily used on systems which also have front panel control (allowing the operator to interrupt, single step, perform read/write operations etc. on the bus master):

XRDY and pRDY These signals allow bus slaves to synchronise with bus masters and request operations of the permanent master.

MWRT This is a control signal used to indicate a memory write operation.

There are four lines which are used to tri-state the bus drivers, for example, during DMA operations:

| SDSB  | Status disable   |

|-------|------------------|

| CDSB  | Control disable  |

| ADSB  | Address disable  |

| DODSB | Data out disable |

System reset signals:

pRESET This is the reset signal for all bus masters.

POC Power-On-Clear, this is only asserted when the power is switched on and it also asserts pRESET.

## **CROMEMCO SINGLE CARD COMPUTER**

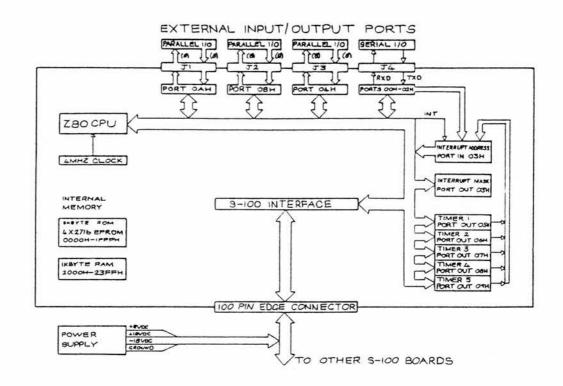

The Cromemco Single Card Computer (SCC) is a Zilog Z80A based S-100 interface board and can be used as a self contained development system. It allows parallel and serial input/output and provides on board sockets for eight kilobytes of user programmable EPROM memory. Figure 2.1 shows the Single Card Computer block diagram. Table 2.1, which is a subset of Table 1.1, shows S-100 bus connections of the Single Card Computer.

| 1                | +8V   | 26 | pHLDA         | 51 | +8V    | 76  | pSYNC |

|------------------|-------|----|---------------|----|--------|-----|-------|

| 2                | +18V  | 27 |               | 52 | -18V   | 77  | pWR   |

| 3                | XRDY  | 28 |               | 53 |        | 78  | pDBIN |

| 2<br>3<br>4<br>5 |       | 29 | A5            | 54 |        | 79  | A0    |

| 5                |       | 30 | A4            | 55 |        | 80  | A1    |

| 6                |       | 31 | A3            | 56 |        | 81  | A2    |

| 7                |       | 32 | A15           | 57 |        | 82  | A6    |

| 8                |       | 33 | A12           | 58 |        | 83  | A7    |

| 9                |       | 34 | A9            | 59 |        | 84  | A8    |

| 10               |       | 35 | DO1           | 60 |        | 85  | A13   |

| 11               |       | 36 | DO0           | 61 |        | 86  | A14   |

| 12               | NMI   | 37 | A10           | 62 |        | 87  | A11   |

| 13               | '     | 38 | DO4           | 63 |        | 88  | DO2   |

| 14               |       | 39 | DO5           | 64 |        | 89  | DO3   |

| 15               |       | 40 | DO6           | 65 | MREQ   | 90  | DO7   |

| 16               |       | 41 | DI2           | 66 | RFSH   | 91  | DI4   |

| 17               |       | 42 | DI3           | 67 |        | 92  | DI5   |

| 18               | SDSB  | 43 | DI7           | 68 | MWRT   | 93  | DI6   |

| 19               | CDSB  | 44 | sM1           | 69 |        | 94  | DI1   |

| 20               |       | 45 | sOUT          | 70 |        | 95  | DI0   |

| 21               |       | 46 | sINP          | 71 |        | 96  | sINTA |

| 22               | ADSB  | 47 | <b>s</b> MEMR | 72 | pRDY   | 97  | sWO   |

| 23               | DODSB | 48 | sHLTA         | 73 | PINT   | 98  | 4MHz  |

| 24               | φ     | 49 | CLOCK         | 74 | PHOLD  | 99  | POC   |

| 25               |       | 50 | GND           | 75 | PRESET | 100 | GND   |

## Table 2.1 : SCC S-100 Bus Signals

As mentioned in Chapter 1, the S-100 bus signals were designed for use with the Intel 8080 microprocessor. There is a substantial difference between the 8080 and Z80A control lines, but the SCC board is designed to interpret the important S-100 "8080-like" bus functions.

## Figure 2.1 : Single Card Computer Block Diagram

The SCC can be grouped into eight parts:

Power supply Clocks Z80A Central Processing Unit System reset Memory Input/output ports Interrupts Timers

## 2.1 POWER SUPPLY

The SCC board requires three unregulated voltages:

+8VDC @ 1.75A +18VDC @ 100mA -18VDC @ 50mA

These voltages are regulated on the SCC board to +5VDC, +12VDC and -5VDC respectively. The +5VDC provides power to the TTL logic and the 5501 UART. The +12VDC and -5VDC voltages provide power to the UART.

## 2.2 CLOCKS

There is an 8MHz crystal on the SCC board which is used to control the internal SCC timing functions. This frequency is then halved to provide the 4MHz to the Z80A CPU clock input, and to the S-100  $\phi$  bus line. Other SCC devices use the complement of the 4MHz signal as a reference. The 4MHz frequency is halved again to supply a 2MHz signal to the S-100 CLOCK bus line, and to both of the 5501 UART clock inputs ( $\phi_1$  and  $\phi_2$ ).

The S-100 bus 4MHz line (pin 98) is a Cromemco Z80A system function. This signal is used to show whether the system is running at 4MHz (logic 1) or 2MHz (logic 0). This line is pulled high on the SCC board.

## 2.3 Z80A CPU

The Z80A Central Processing Unit allows direct addressing of up to 64 Kilobytes of memory, 256 input ports and 256 output ports. The Z80A instruction set contains 158 instructions, including the 78 instructions of the 8080A.

## **Z80A REGISTERS**

The Z80A contains eighteen 8 bit registers, four 16 bit registers and two interrupt status flip-flops. These can be divided into groups as shown in the following tables.

#### Main 8 Bit Register Set

Alternate 8 Bit Register Set

| D (General)E (General)D (General)E (General)H (General)L (General)H' (General)L' (General) | A (Accumulator)<br>B (General)<br>D (General)<br>H (General) | F (Flag)<br>C (General)<br>E (General)<br>L (General) | A' (Accumulator)<br>B' (General)<br>D' (General)<br>H' (General) | F' (Flag)<br>C' (General)<br>E' (General)<br>L' (General) |  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------|--|

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------|--|

- A, A' The accumulator holds the results of logical and arithmetic operations.

- F,F' The flag register indicates the conditions of the last operation (eg. if the result was zero).

- B,B',C,C',D,D', These remaining general purpose registers can either be used as E,E',H,H',L,L' twelve 8 bit registers, or as six 16 bit register pairs (BC, DE etc.).

### Special Purpose 16 Bit Registers

| IX (Index Register) | IY (Index Register)  |

|---------------------|----------------------|

| SP (Stack Pointer)  | PC (Program Counter) |

- IX, IY The index registers are used to hold the base address when using indexed addressing mode.

- SP The stack pointer register holds the address of the current top of the stack. The stack is a temporary data storage area.

- PC The program counter is the register which holds the address of the instruction which is being fetched from memory. After the contents of the counter are transferred to the address bus, the program counter is automatically incremented. If the instruction being executed causes a program jump, the new address is written over the address in the counter register.

## Special Purpose 8 Bit Registers

| I (Interrupt | R (Refresh |  |

|--------------|------------|--|

| Register)    | Register)  |  |

- I The interrupt register is used when the Z80A CPU is operated in a mode which will respond to an interrupt with an indirect call to any memory location. Servicing interrupt requests in this way means that the time taken to access the interrupt routine can be minimised, as the routine can be stored anywhere in memory.

- R The refresh register is used to generate the memory refresh address when dynamic memories are being used in the system.

#### Interrupt Status Flip-Flops

#### Interrupt Mode Flip-Flops

| IFF1 | IFF2 | IMFa | IMFb |

|------|------|------|------|

|------|------|------|------|

IFF1, IFF2 The interrupt status flip-flops and the interrupt mode flip-flops are the registers which help to ascertain the current interrupt mode of the Z80A CPU, (Mode 0, Mode 1 or Mode 2).

## **Z80A ADDRESS BUS AND DATA BUS**

The Z80A has a 16 bit, (tri-state output), address bus and an 8 bit, (tri-state input/output), data bus. The lines of these buses can be in three different states, logic 1, logic 0 or in a high impedance state. When the buses of the Z80A CPU are in the high impedance state they appear to be disconnected from the other devices which utilise the bus. This allows the other logic circuitry to use the bus without any confusion of the signals.

The S-100 address bus, A0-A15, is driven from the Z80A address bus, A0-A15. The two buses are connected together, via two tri-state drivers. The S-100 address bus drivers can be put into a high impedance state during direct memory access operations by asserting the S-100 bus signal ADSB. The Z80A address bus controls the SCC memory and input/output ports, as described in Chapters 2.6 and 2.7.

The S-100 data out bus, DO0-DO7, is driven from the Z80A data bus, D0-D7, via a tri-state driver. Similarly, the Z80A data bus receives data from the S-100 data in bus, DI0-DI7, via a tri-state buffer. The data output driver can be disabled (ie. tri-stated) during direct memory access operations by asserting the S-100 bus signal DODSB.

## **Z80A CONTROL INPUT SIGNALS**

NMI (non-maskable interrupt) is a buffered version of the S-100 bus NMI signal. Similarly, BUSRQ (bus request) is the buffered version of S-100 bus signal  $\overline{p}HOLD$ . The Z80A WAIT (wait) input is used to indicate to the CPU that the addressed memory or input/output devices are not ready for a data transfer. The CPU stays in the wait state as long as this signal is asserted. INT (interrupt request) is generated by input/output devices. The CPU will service the interrupt at the end of the current instruction if the internal software controlled interrupt enable flip-flop (IFF) is enabled. RESET is used to initialise the CPU, (see Z80A Reset section for more information).

## **Z80A CONTROL OUTPUT SIGNALS**

The Z80A control output lines are logically combined to generate S-100 bus control signals. S-100 signals sM1, pHLDA and sHLTA are the logical inversion of MI (machine cycle one), BUSAK (bus acknowledge) and HALT (halt state) respectively. S-100 MREQ is a buffered version of the Z80A MREQ (memory request) signal. Similarly, S-100 RFSH is the buffered version of Z80A signal RFSH (refresh). S-100 pSYNC which signals the beginning of a new machine cycle is clocked high by a falling edge of either MREQ or IORQ and is clocked back low by the next rising edge of phi. The remaining S-100 control lines are derived from the Z80A outputs as shown:

> sINP = IORQ + RD sOUT = IORQ + WR  $\overline{sWO} = sOUT + (RFSH \cdot RD \cdot MREQ)$  sMEMR = MREQ + RD  $sINTA = (External Priority) \cdot (MI + IORQ)$  pDBIN = RD + sINTA $\overline{pWR} = WR(Delayed)$

$\overline{pWR}$  is delayed so sOUT has time to stabilise before the pWR low pulse is used as a data strobe. All of these lines can be disabled during DMA by asserting S-100 bus lines  $\overline{SDSB}$  and  $\overline{CDSB}$ .

## **Z80A RESET**

The Z80A CPU is reset when the RESET input is asserted (0V) for at least three clock cycles (600nS). This resets the interrupt enable flip-flop, clears the program counter and registers I and R and sets the interrupt status flip-flops to Mode 0. During the reset time the address bus and the data bus go into a high impedance state and all control output signals go to the inactive state. When the Z80A is reset the program counter is set to 0000H, and program execution is started from memory location 0000H.

## 2.4 SYSTEM RESET

On power up the SCC circuitry automatically asserts the S-100 POC (Power-On-Clear) line, this also asserts the S-100  $\overline{p}$ RESET line. This resets the Z80A, by asserting RESET, and puts the SCC into a known state with the on board memory enabled. The same resetting of the SCC and Z80A occurs when the S-100  $\overline{p}$ RESET signal is asserted by an external source. Any other device can use the S-100  $\overline{p}$ RESET bus line to reset to a known state.

## 2.5 SCC MEMORY

The SCC has space for 8 kilobytes of 2716 EPROM memory (in sockets ROM0, ROM1, ROM2 and ROM3) and 1 kilobyte of 4045 static RAM. The memory address map is shown in the following table.

## SCC Memory Map

| ROM0 (2K)       | 0000H - 07FFH |

|-----------------|---------------|

| ROM1 (2K)       | 8000H - 0FFFH |

| ROM2 (2K)       | 1000H - 17FFH |

| ROM3 (2K)       | 1800H - 1FFFH |

| RAM             | 2000H - 23FFH |

| External Memory | 2400H - FFFFH |

Additional memory can be installed in the SCC controlled system by plugging ROM or RAM boards into the S-100 bus.

ROM0 contains the assembled SCSI INTERFACE program (see Appendices A and B) which is automatically entered when the SCC is powered up or when the S-100  $\overline{pRESET}$  line is pulled low, causing the Z80A to reset the program counter to 0000H and start program execution.

## MEMORY SELECTION

The memory select signals are controlled by a standard 4 line to 10 line (BCD to DECIMAL) decoder chip as shown by the table below.

#### **INPUTS OUTPUTS** B D σ T 4 DEVICE A C 2 3 A11 A12 SELECTED A13 0 0 0 0 0 1 1 1 1 ROM0 0 0 0 1 1 1 0 1 1 ROM1 ROM<sub>2</sub> 0 1 0 0 1 1 0 1 1 1 1 0 0 1 1 1 0 1 ROM3

## **ROM Memory Select Logic**

## **RAM Memory Select Logic**

|          | INP      | UTS      |   |   | 0 | UTPU | ГS |   | ]  |                    |

|----------|----------|----------|---|---|---|------|----|---|----|--------------------|

| A<br>A11 | B<br>A12 | C<br>A13 | D | σ | T | 2    | 3  | 4 | EN | DEVICE<br>SELECTED |

| 0        | 0        | 1        | 0 | 1 | 1 | 1    | 1  | 0 | 0  | RAM                |

In both of the above memory select logic tables, decoder inputs A, B and C are A11, A12 and A13 respectively. Decoder input D is used as an active low enable signal. D is low when the SCC memory disable option is inactive, MI or MREQ is active (logic 0), IORQ is not active (logic 1), A14 and A15 are low.

In the RAM select logic table, EN is the logical OR of A10 and the decoder output 4.

ROM0-ROM3 are selected with the appropriate address on A11-A13 and decoder input D active (logic 0). The SCC RAM is selected with the appropriate address on A10-A13 and decoder input D active (logic 0).

## 2.6 SCC INPUT/OUTPUT PORTS

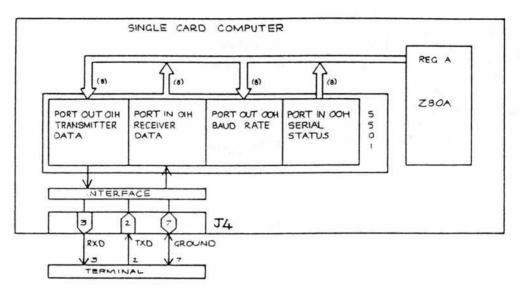

The SCC has three 8 bit parallel input/output ports, with separate input data lines and output data lines, on connectors J1, J2 and J3 (addressed at 0AH, 0BH and 04H respectively). Port 04H is an integral part of the 5501 UART and ports 0AH and 0BH are driven from the Z80A data bus via latches. The parallel input/output ports are not used in this project and are only mentioned briefly. The serial input/output port found on connector J4, addressed at 00H-02H, is used to connect a VDU terminal to the SCC. The VDU terminal is used to input data into the SCC and display the output from the SCC.

Data is received from and transmitted to the terminal, (via connector J4), from the Z80A (register A). The parallel CPU data is converted to the serial terminal data, and vice versa, by the 5501 Universal Asynchronous Receiver Transmitter (UART). The UART also supplies the serial status data and the serial control data.

The SCC TTL signals (0V or 5V) are converted to the terminal RS232 ( $\pm 12V$ ) signals, and from RS232 to TTL, by the interface on the SCC. See figure 2.2 which shows the serial signal paths of the SCC and the terminal connection.

The input/output select logic, for the ports and the UART, is controlled by a Cromemco custom PROM as shown by the tables below. The inputs to the PROM are, from the address bus, A0-A3 and, from the Z80A CPU, WR. The CS input is low when A4-A7 are low, IORQ is active, and MI is inactive.

There are eight output lines from the PROM, Y1-Y8. Y1 and Y2 are used as an active high strobe for 0BH and 0AH respectively. Y3 is an active low enable for the 5501 UART. Y4-Y7 select a 5501 UART function by driving its A0-A3 address lines as shown in the table below.

| D7 | D6 | D5     | D4 | D3           | D2     | D1 | D0 |

|----|----|--------|----|--------------|--------|----|----|

|    |    | DATA I |    | OM TER<br>Γ> | RMINAL |    |    |

When an IN A,(01H) instruction is executed, an assembled data byte (D0 - D7) is read into the Z80A (register A), from the the UART receiver data port (ie. the terminal). The Z80A knows when there is valid data available by testing the serial status port, bit RDA.

All bits are used in relation to this project.

## **Transmitter Data Port**

| D7 | D6 | D5   | D4 | D3      | D2   | D1 | D0 |

|----|----|------|----|---------|------|----|----|

|    |    | DATA |    | ΤΟ TERM | INAL |    |    |

Data is written from the Z80A (register A) into the transmitter data port (D0 - D7) when the Z80A executes an OUT (01H), A. The Z80A is programmed to recognise when to send the data byte, by testing the serial status port, bit TBE.

All bits are used in relation to this project.

## **Command Register Port**

| D7          | D6          | D5  | D4  | D3  | D2  | D1  | D0  |

|-------------|-------------|-----|-----|-----|-----|-----|-----|

| NOT<br>USED | NOT<br>USED | TB5 | HBD | INE | RS7 | BRK | RES |

The UART is configured when an OUT (02H), A instruction is executed (register A containing the data). Only four of the command register port bits have any effect on the serial port - HBD, INE, BRK and RES.

- HBD (D4) High Baud. Setting this bit to logic 1 multiplies the UART clock frequency by eight, which causes the serial port baud rate to multiply by eight (eg. 1200 baud becomes 9600 baud).

- INE (D3) INTA Enable. When this bit is reset to logic 0 the UART ignores the INTA (interrupt acknowledge) cycles. The UART will recognise the INTA cycles and service the interrupt when this bit is set to logic 1.

- BRK (D1) Break. When this is reset to logic 0 the serial transmitter operates normally however, when set to logic 1 the serial transmitter output is latched in the low (spacing) state.

- RES (D0) UART Reset. When this bit is set to logic 1 the serial status port bit, RDA, is reset to logic 0 and the serial receiver goes into the search for a new character mode (not affecting the contents of the receiver data port). Also, the serial status register port, bit TBE, is set to logic 1 and the serial transmitter output goes high (marking). Once this happens RES will reset to logic 0 and the UART will be ready to perform serial input/output operations.

Only bits D4 (HBD) and D0 (RES) are used in relation to this project.

#### Interrupt Address Port

| D7 | D6 | D5             | D4 | D3             | D2 | D1 | D0 |

|----|----|----------------|----|----------------|----|----|----|

| 1  | 1  | L <sub>2</sub> | L  | L <sub>o</sub> | 1  | 1  | 1  |

When the UART interrupt address port is read by execution of an IN A,(03H) instruction, the Z80A (register A) contains the coding of the source of the interrupt request (eg. if the contents are 07EH then is RDA requesting service).

This port is not implemented in relation to this project.

#### **Interrupt Mask Port**

| D7         | D6         | D5  | D4  | D3         | D2  | D1         | D0         |

|------------|------------|-----|-----|------------|-----|------------|------------|

| TIMER<br>5 | TIMER<br>4 | TBE | RDA | TIMER<br>3 | INT | TIMER<br>2 | TIMER<br>1 |

The UART interrupt mask port is configured an OUT (03H), A instruction is executed by the Z80A (register A containing the data).

When the bit is reset to logic 0, the source cannot issue an interrupt request. When the bit is set to logic 1 the source can issue an interrupt request. TBE (D5) and RDA (D4) cannot be disabled in this way.

This port is not implemented in relation to this project.

## 2.7 SCC INTERRUPTS

The SCC has ten interrupt sources which can be grouped as follows:

| S-100 Interrupts | NMI is connected directly to the Z80A NMI input and is the only interrupt which cannot be software disabled. pINT is channelled into the Z80A INT input and is only enabled after the Z80A executes an EI instruction.                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UART Interrupts  | TIMER1-TIMER5, INT, RDA and TBE are all channelled into the Z80A INT input. For any of these interrupts to be enabled the correct interrupt mask port code must be present in addition to the interrupts being enabled by execution of the Z80A EI instruction. |

The interrupts are not utilised in relation to this project.

## 2.8 SCC TIMERS

The UART contains five timers, TIMER1-TIMER5, which can be enabled and disabled by the UART interrupt mask port. There is a port assigned to each of the timers (05H - 09H) which can be loaded with a delay count (maximum value of 0FFH). This delay count is then decremented either every 64 micro-seconds (if command register port HBD is reset) or every 8 micro-seconds (if HBD is set).

If the interrupts are disabled when the delay count reaches zero the UART serial status port, bit IPG, is set to logic 1. The Z80A can determine the timer which is requesting service and reset IPG to logic 0 by reading the UART interrupt address port. This method does not enter an INTA cycle as only the SCC input ports are being used, not the Z80A INT input. If the interrupts are enabled and UART command register port, bit INE, is set to logic 1 when the delay count reaches zero, the Z80A is interrupted. The Z80A will then execute the timer unique RST instruction in response to the Z80A INTA cycle.

If the interrupts are enabled and UART command register port, bit INE, is reset to logic 0 when the delay count reaches zero, the Z80A is interrupted. The Z80A will initiate an interrupt service routine which will read the interrupt address port to identify the source.

The timers are not utilised in relation to this project.

## **2.9 UART CONFIGURATION**

Before the serial input/output port is used the UART must be configured by writing into register A and issuing an OUT (02H), A instruction. The correct baud rate must also be set by writing into register A and issuing an OUT (00H), A instruction.

The following shows the part of the main program which is used to configure the UART. Refer to the UART ports descriptions for full details on the ports mentioned in the description of the program.

## **BAUD RATE TABLE**

This shows the table of bytes for the different baud rates. When the program is assembled and written into the EPROM, the binary number are stored as hex bytes in consecutive locations with a label (baudrs).

| db | 10010000b                        | ; 2400 / 19,200                                                                               |

|----|----------------------------------|-----------------------------------------------------------------------------------------------|

| db | 1100000b                         | ;9600/76,800                                                                                  |

| db | 10100000b                        | ; 4800 / 38,400                                                                               |

| db | 10010000b                        | ; 2400 / 19,200                                                                               |

| db | 10001000b                        | ; 1200 / 9,600                                                                                |

| db | 10000100b                        | ; 300/2,400                                                                                   |

| db | 10000010b                        | ; 150/1,200                                                                                   |

| db | 0000001b                         | ; 110/880                                                                                     |

|    | db<br>db<br>db<br>db<br>db<br>db | db 11000000b<br>db 10100000b<br>db 10010000b<br>db 10001000b<br>db 10000100b<br>db 100000100b |

The terminal can be operating at any one of a number of baud rates, as shown by the table above. The UART command register port, bit HBD determines which range of baud rates are valid. When HBD is set to 0, the range is 110 baud to 9600 baud. When HBD is set to 1, the range is 880 baud to 76,800 baud. The first value in the table, 2400/19,200, is the normal setting for the terminal, if this is not correct, the other values will be tried.

When the boards are powered up, the user must press the carriage return key (ASCII value - 0DH) several times to allow the baud rate of the terminal and the baud rate of the SCC to be matched. The program does this as shown below.

## **PROGRAM LISTING**

## Main Program

| Line 1  |       | ld   | hl,baudrs |

|---------|-------|------|-----------|

| Line 2  |       | ld   | c,00H     |

| Line 3  |       | ld   | a,11h     |

| Line 4  | baud1 | out  | (02H),a   |

| Line 5  |       | outi |           |

| Line 6  |       | call | gbyte     |

| Line 7  |       | call | gbyte     |

| Line 8  |       | and  | 7fh       |

| Line 9  |       | ср   | Odh       |

| Line 10 |       | ld   | a,1       |

| Line 11 |       | jr   | nz,baud1  |

Gbyte Subroutine

| Line S1 | gbyte | in  | a,(00H) |

|---------|-------|-----|---------|

| Line S2 | •••   | bit | 6,a     |

| Line S3 |       | jr  | z,gbyte |

| Line S4 |       | in  | a,(01H) |

| Line S5 |       | ret |         |

## **PROGRAM DESCRIPTION**

Line 1 to Line 3 sets up the contents of the HL, C and A registers.

Register pair HL is pointing to the first baud rate in the table.

Register C contains the address of the UART baud rate port.

Register A contains reset bit and high baud for sending to the UART command register port.

Line 4 outputs the contents of register A, (00010001 in binary notation), to the UART command register port (02H). This configures and resets the UART. Note that this line has a label (baud1). If the correct baud rate is not found the first time, the program will jump back to here and reset the UART. The program will continue looping round to Line 4 until the correct baud rate is found. The UART command register will contain the following.

| D7          | D6          | D5  | D4  | D3  | D2  | D1  | D0  |

|-------------|-------------|-----|-----|-----|-----|-----|-----|

| NOT<br>USED | NOT<br>USED | TB5 | HBD | INE | RS7 | BRK | RES |

| 0           | 0           | 0   | 1   | 0   | 0   | 0   | 1   |

Four of these bits have an effect on the serial input/output port: HBD, INE, BRK and RES.

HBD=1, serial port baud rate to multiplies by eight (eg. 2400 baud becomes 19,200 baud).

INE=0, interrupt acknowledge (INTA) cycles ignored by UART.

BRK=0, serial transmitter operates normally.

RES=1, reset UART.

Line 5 outputs the contents of the memory location addressed by HL (first baud rate), to the address contained in register C, (UART baud rate port) and then increments HL. HL is then pointing to the next baud rate in the table. For the first baud rate in the table, the UART baud rate port contains the following.

| D7           | D6              | D5              | D4              | D3             | D2            | D1            | D0          |

|--------------|-----------------|-----------------|-----------------|----------------|---------------|---------------|-------------|

| STOP<br>BITS | 9600/<br>76,800 | 4800/<br>38,400 | 2400/<br>19,200 | 1200/<br>9,600 | 300/<br>2,400 | 150/<br>1,200 | 110/<br>880 |

| 1            | 0               | 0               | 1               | 0              | 0             | 0             | 0           |

This sets the baud rate port to a baud rate of 19,200, (HBD=1 UART command register port), with 1 stop bits. For subsequent baud rates, HBD=0 in the UART command register port, therefore the lower values are active.

Lines 6 and 7 call the gbyte subroutine. This subroutine is called twice to stop any phase match error. The first call of the gbyte subroutine is being ignored in this description as explained above. The second call of the gbyte subroutine performs a read from the terminal, via the SCC serial port, using the carriage return characters which the user is sending to determine the baud rate setting of the terminal.

Line S1 of the gbyte subroutine inputs a data byte from the UART serial status port, (00H), into register A. Note that this line has a label (gbyte). This label is not only used for the call instruction from the main program, it is also used by the subroutine itself.

Line S2 tests bit 6 of register A, UART serial status port bit RDA. A logic 0 in this bit, (no data byte available), sets the zero flag. A logic 1 in this bit, (data byte available), does not set the zero flag. The UART serial status port is shown below.

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| TBE | RDA | IPG | TBE | RDA | SRV | ORE | FME |

| Х   | 0/1 | Х   | X   | X   | X   | Х   | X   |

Line S3 causes the program to jump back to Line S1 if there is no data byte available. The program will continue looping in this manner until there is a data byte available.

When there is a data byte available, Line S4 reads it from the receiver data port, (address 01H), and stores it in register A. Line S5 returns to the main program, (Line 8).

Line 8 performs a logical AND between register A and 7FH, this masks off bit D7 of the receiver data port because only bits D0 to D6 are valid.

Line 9 compares the contents of register A, (receiver data port), with 0DH, (carriage return character). If the data byte in register A is 0DH the zero flag is set, otherwise the zero flag is not set. The setting of the zero flag signifies that the baud rate of the terminal and the baud rate of the SCC are matched.

Line 10 loads register A with 1, (00000001 in binary notation), which is used to reset the UART command register port if a 0DH is not recognised, (incorrect baud rate).

Line 11 tests the zero flag and depending on its value, either continues with the program or jumps back to Line 4. If the baud rates match, the zero flag will be set and the main program will continue. If the baud rates do not match, the zero flag will not be set and there will be a jump back to Line 4, (reset UART command register port), where the next value in baud rate table will be tried. The program continues in this manner until the baud rate of the terminal and the baud rate of the SCC are matched.

## CHAPTER 3

## THE SMALL COMPUTER SYSTEM INTERFACE (SCSI)

In this chapter SCSI is discussed with reference to the RODIME RO652 hard disk drive which was used in this project. SCSI supports both block and character transfer, the RO652 uses the block method. For more detailed information on SCSI, the American National Standards Institute document X3T9 should be referred to.

The theory of bus structure is based on a system originally developed in the 1960's and 1970's for use in mainframe computers. This concept was improved on and was introduced as the Shugart Associated Standard Interface (SASI). SASI was then offered to the American National Standards Institute (ANSI) as the basis for a new industry standard. The Small Computer System Interface (SCSI) was the name chosen by ANSI and the X3T9 specification was issued in the early 1980's.

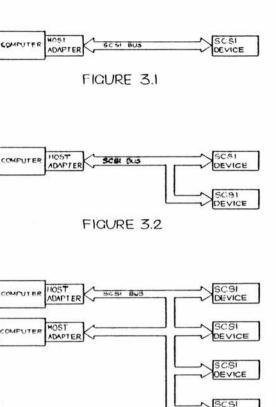

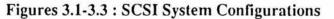

The SCSI interface is an eight bit, eight port intelligent bus. RO652 bus transfers are asynchronous and follow a defined REQ/ACK handshake protocol. The input/output bus structure enables intelligent peripherals to communicate with multiple hosts over a single bus and allows these peripherals to be used by one or more host computers attached to the same bus. Communication on the SCSI bus uses the initiator/target framework, where the initiator is the device which requests that an operation be performed by another device and the target is the device which performs an operation when requested to do so by an initiator. Up to eight SCSI devices can be supported in any combination on the bus. There are three principal SCSI system configurations: single initiator/single target (figure 3.1); single initiator/multi target (figure 3.2) and multi initiator/multi target (figure 3.3). The main advantage of the SCSI bus system is that several tasks can be interleaved at the same time (figure 3.4).

SCSI can also operate in a synchronous data transfer mode, which is faster than the asynchronous mode, due to reduced handshaking. Synchronous data bus transfers can only be used if previously agreed by both the initiator and the target, using a Synchronous Data Transfer Request command.

HOST

OMPUTER

DEVICE

SCSI

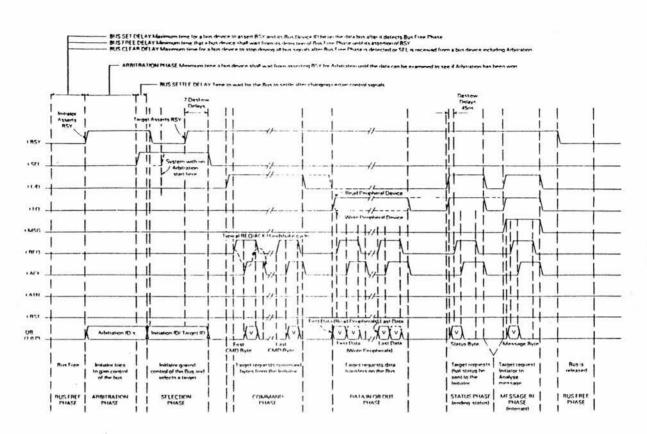

Arbitration allows a number of peripheral devices to be attached to the bus and makes it possible for one SCSI device to gain control of the bus and assume the role of an initiator or a target. To gain control of the bus, a device waits for a bus free state and asserts its own SCSI ID. After waiting for at least an arbitration delay the SCSI device examines the data bus, if there is a higher SCSI ID present the device has lost control, if no higher SCSI ID is present the device has won control of the bus. Figure 3.5 and figure 3.6 show the sequence of bus phases for arbitrating and non-arbitrating devices.

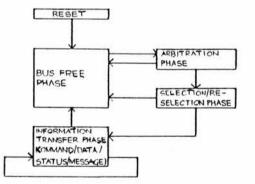

Figures 3.5-3.6 : SCSI Bus Phases

## **3.1 HARDWARE**

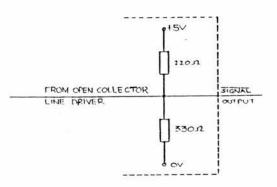

SCSI devices are daisy chained together using a 50 way cable. The RO652 hard disk drive uses the single ended driver alternative, which gives a maximum cable length of six metres. The differential pair driver alternative has a maximum cable length of 25 metres and is normally used where the SCSI device has to be some distance from the host. Both ends of the bus cable must be terminated correctly, with 220 ohms to +5V and 330 ohms to ground,

on all of the signal lines. Figure 3.7 shows an example of correct signal termination. Single ended drivers and differential pair drivers cannot be used on the same bus. All signals on the SCSI bus are active low and use open collector drivers. SCSI bus signals use negative logic, this means that a false/deasserted signal on the SCSI bus is +5 volts and a true/asserted signal is 0 volts.

Figure 3.7 : SCSI Bus Termination

The SCSI interface is a bidirectional bus interface which transfers data asynchronously. The fifty way SCSI bus consists of eighteen signal lines: nine control signals used to co-ordinate data transfer between the host system and the disk drive and nine data bus signals used as an eight-bit bidirectional data bus with parity. The following table shows the SCSI single ended option pin numbers and names for the RO652.

## SCSI BUS SIGNALS

| 1  | GND | 27 | GND | 2  | DBO     | 28 | NC  |

|----|-----|----|-----|----|---------|----|-----|

| 3  | GND | 29 | GND | 4  | DBI     | 30 | NC  |

| 5  | GND | 31 | GND | 6  | DB2     | 32 | ATN |

| 7  | GND | 33 | GND | 8  | DB3     | 34 | NC  |

| 9  | GND | 35 | GND | 10 | DB4     | 36 | BSY |

| 11 | GND | 37 | GND | 12 | DB5     | 38 | ACK |

| 13 | GND | 39 | GND | 14 | DB6     | 40 | RST |

| 15 | GND | 41 | GND | 16 | DB7     | 42 | MSG |

| 17 | GND | 43 | GND | 18 | DBP     | 44 | SEL |

| 19 | GND | 45 | GND | 20 | NC      | 46 | C/D |

| 21 | GND | 47 | GND | 22 | NC      | 48 | REQ |

| 23 | GND | 49 | GND | 24 | NC      | 50 | I/0 |

| 25 | NC  |    |     | 26 | TERMPWR |    |     |

TERMPWR

Terminator power is a +4.0VDC - +5.25VDC signal which is provided on the SCSI bus by the RO652. GND GROUND NC No Connection

DB0-DB7, DBP These nine lines, data bit 0-data bit 7, and a data parity bit form the data bus. Data bit 7 is the most significant bit and has the highest priority during an arbitration phase. Data bit 0 is the least significant bit and has the lowest priority during an arbitration phase. Parity is odd in the SCSI system and can either be enabled on all devices connected to the SCSI bus or disabled on all devices. The RO652 does not support parity.

## **Control Lines**

- ATN Attention indicates to the target that the initiator has a message to send.

- BSY Busy indicates that the bus is in use.

- ACK Acknowledge is used with REQ to indicate an acknowledgement of a bus transfer handshake.

- RST Reset is used to clear all activity on the bus.

- MSG Message indicates that the bus is in a message phase.

- SEL Select is used during device-selection phase.

- C/D Control/Data indicates whether control or data information is on the data bus. When this signal is true control information is on the bus.

- **REQ** Request is used with ACK to request a bus transfer handshake.

- I/O Input/Output indicates direction of the data flow on data bus, with respect to the initiator. When this signal is true, data is being inputted to the initiator.

## **3.2 SCSI BUS PHASES**

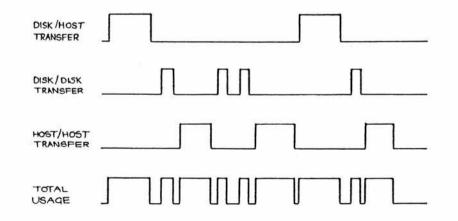

The SCSI bus can be in one of eight phases:

Bus Free Phase Arbitration Phase Selection Phase Reselection Phase Command Phase Data Exchange Phase Status Phase Message Phase

Phases 5, 6, 7 and 8 are collectively known as the Information Transfer Phase.

The following table shows which of the SCSI bus signals the initiator or the target is permitted to source during the specific phase. The SCSI bus signal RST may be sourced by both initiator and target during any phase. No attempt is made here to show if the source is driving the SCSI bus signal asserted, negated, or is passive. All SCSI device drivers that are not active sources are in the passive state.

#### Signal Sources

| Bus Phase                                                                                       | BSY                                                               | SEL                                                           | C/D,I/O<br>MSG,REQ                                             | ACK,ATN                                                                       | DB(7-0,P)                                                                            |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| Bus Free<br>Arbitration<br>Selection<br>Reselection<br>Command<br>Data In<br>Data Out<br>Status | None<br>All<br>I+T<br>I+T<br>Target<br>Target<br>Target<br>Target | None<br>Winner<br>Initiator<br>Target<br>None<br>None<br>None | None<br>None<br>Target<br>Target<br>Target<br>Target<br>Target | None<br>None<br>Initiator<br>Initiator<br>Initiator<br>Initiator<br>Initiator | None<br>SCSI ID<br>Initiator<br>Target<br>Initiator<br>Target<br>Initiator<br>Target |  |

| Message In<br>Message Out                                                                       | Target<br>Target                                                  | None<br>None                                                  | Target<br>Target                                               | Initiator<br>Initiator                                                        | Target<br>Initiator                                                                  |  |

- All The signal is driven by all SCSI devices that are actively arbitrating.

- SCSI ID A unique data bit, the SCSI ID, is driven by each SCSI device that is actively arbitrating; the other 7 data bits are deasserted (ie. not driven) by that device. DBP may be undriven or driven true but can never be driven false during this phase.

- I+T The signal is driven by the initiator, the target or both as specified in the Selection and Reselection Phases.

- Initiator If the signal is driven, it is only driven by the active initiator.

- None The signal is deasserted; that is not be driven by any SCSI device. The bias circuitry of the bus terminators pulls the signal to a false state.

- Winner The signal is driven by the SCSI device that wins arbitration.

- Target If the signal is driven, it is driven only by the active target.

The following descriptions of the phases should be read in conjunction with appendix C.

### **BUS FREE PHASE**

The Bus Free Phase is used to indicate that no device is using the bus. It is caused by BSY and SEL being false, for at least a bus settle delay (400 nanoseconds), and all connected devices releasing control of the bus within a bus clear delay (800 nanoseconds).

### **ARBITRATION PHASE**

The Arbitration Phase is only used in multiple host configurations and is not implemented in relation to this project. The Arbitration Phase is used to avoid bus conflicts. During arbitration, devices try to gain control of the bus by asserting a unique SCSI ID onto one bit of the data bus and releasing the other seven data bits. The device asserting DB7 has the highest priority and the device asserting DB0 has the lowest priority. To arbitrate for control of the bus, the device has to:

Test for a Bus Free Phase, ie. BSY and SEL false for at least a bus settle delay.

After detection of a Bus Free Phase, the device waits for at least a bus free delay.

The device then asserts BSY and its own SCSI ID.

The device then waits for an arbitration delay and examines the SCSI bus. If there is a higher priority SCSI ID bit on the data bus then the device has lost arbitration and has to release BSY and its SCSI ID from the data bus, then wait for the next Bus Free Phase. If there is no higher SCSI ID bit on the data bus the device has won arbitration and asserts SEL to claim the bus and enters the Selection Phase.

### SELECTION PHASE

For single initiator systems the Selection Phase is entered after the Bus Free Phase. During this phase:

The initiator selects the SCSI target to communicate with by asserting its own address and the address of the target onto the bus.

After a delay the initiator asserts SEL.

The target will then assert BSY.

Then the initiator releases SEL.

BSY remains asserted until the next Bus Free Phase, when the target will release it.

### **RESELECTION PHASE**

The Reselection Phase allows the target to reconnect to an initiator to continue an operation that was previously started by the initiator, but was suspended by the target, i.e. the target disconnected by allowing a Bus Free Phase to occur before the operation was finished. Reselection can only be used in systems that have an Arbitration Phase implemented. The Reselection Phase is not supported by the RO652 and is not used in this project.

### INFORMATION TRANSFER PHASE

There are four information phases, as shown below. Note that the Data Phase is subdivided into a Data In Phase and a Data Out Phase, and that the Message Phase is subdivided into a Message In Phase and a Message Out Phase.

Command Phase Status Phase Data Phase: Message Phase:

Data In Phase Data Out Phase Message In Phase Message Out Phase The SCSI bus signals MSG, C/D and I/O are used to distinguish between the different Information Transfer Phases as shown in the table below. These three signals are all driven by the target device, which therefore controls the SCSI bus and all phase changes. The Target can also cause a Bus Free Phase by releasing MSG, C/D, I/O and BSY.

| MSG    | C/D | I/O | Phase Name  | Direction Of Transfer |  |

|--------|-----|-----|-------------|-----------------------|--|

| 0      | 0   | 0   | Data Out    | Initiator -> Target   |  |

|        | Ō   | 1   | Data In     | Target -> Initiator   |  |

| 0<br>0 | 1   | 0   | Command     | Initiator -> Target   |  |

| 0      | 1   | 1   | Status      | Target -> Initiator   |  |

| 1      | 0   | 0   | Reserved    | Ŭ                     |  |

| 1      | 0   | 1   | Reserved    |                       |  |

| 1      | 1   | 0   | Message Out | Initiator -> Target   |  |

| 1      | 1   | 1   | Message In  | Target -> Initiator   |  |

Once the Information Transfer Phase is complete the bus returns to the Bus Free Phase.

# **Command Phase**

This phase follows the Selection Phase and allows the target to obtain the command information from the initiator.

The Command Phase is entered when BSY and C/D are asserted and MSG, I/O, SEL and ATN are deasserted.

The target waits for a bus settle delay and asserts REQ to request the first byte of the Command Descriptor Block (See Chapter 3.4).

The initiator places the first byte on the bus and asserts ACK.

The Target reads the byte, then releases REQ.

The initiator will then release ACK.

The first byte is now transferred and the target will continue to request additional bytes until the complete Command Descriptor Block has been transferred and the Command Phase has ended.

## **Data Phase**

This phase allows the exchange of data between the target and the initiator.

### **Data In Phase**

The Data In Phase allows data to be transferred from the initiator to the target. The Data In Phase is entered when BSY is asserted and MSG, C/D and I/O are deasserted.

The target asserts REQ to request the first data byte.

The initiator places the first data byte on the bus and asserts ACK.

The Target reads the byte, then releases REQ.

The initiator will then release ACK.

The first data byte is now transferred and the target will continue to request additional data bytes until the last data byte has been transferred.

### **Data Out Phase**

The Data Out Phase allows data to be transferred to the initiator from the target. The Data Out Phase is entered when BSY and I/O are asserted and  $\overline{MSG}$  and  $\overline{C}/D$  are deasserted.

The target asserts REQ and the initiator reads the first data byte from the target.

The initiator asserts ACK.

The Target releases the data bus and REQ.

The initiator will then release ACK.

The first data byte is now transferred and the target will continue to request that the initiator reads the data until the last data byte has been transferred.

### **Status Phase**

The Status Phase allows the target to request that the initiator reads its Status information. (Chapter 3.4)

The Status Phase is entered when command execution is complete or an error that cannot be recovered from occurs. BSY, C/D and I/O are asserted and SEL and MSG are deasserted.

The target puts the Status Byte on the bus and asserts REQ.

The initiator reads the byte and asserts ACK.

This causes the target to release REQ.

The initiator will then release ACK.

### **Message Phase**

This phase allows the transfer of a Message information. The first byte transferred can be a single Message Byte (Chapter 3.4) or the first byte of a multiple-byte message.

#### Message In Phase

The Message In Phase allows a Message Byte to be read from the target by the initiator. The Message In Phase signals the end of an operation and is entered when BSY, MSG, C/D and I/O are are asserted.

The target puts the Message Byte on the bus and asserts REQ.

- 36 -

The initiator reads the byte and asserts ACK.

This causes the target to release REQ.

The initiator will then release ACK.

The Message In Phase terminates when MSG is deasserted.

### **Message Out Phase**

The Message Out Phase is not supported by the RO652 and is not used in this project.

### **3.3 SCSI BUS CONDITIONS**

The SCSI bus has two asynchronous conditions, the Attention Condition and the Reset Condition. These cause the SCSI device to perform certain actions and can alter the phase sequence.

### ATTENTION CONDITION

The Attention Condition allows an initiator to inform a target that the initiator has a message ready, (eg. parity error, whereby the target will send the byte again). The target may get this message by performing a Message Out Phase. The initiator creates the Attention Condition by asserting ATN during the Arbitration Phase or Bus Free Phase. This condition is not supported by the R0652 and is not used in this project.

### **RESET CONDITION**

The Reset Condition is used to immediately clear all SCSI devices from the bus. When the RST signal is received by the SCSI device, the device removes all signals that it is currently asserting from the SCSI bus and clears any current commands. A Bus Free Phase always follows a Reset Condition.

### **3.4 SCSI COMMANDS**

The RO652 hard disk drive which was used in this project is always a target. To execute commands the initiator sends a command, using the appropriate Command Descriptor Block, to the target via the host adaptor. The target performs the command and reports its status, (Message Byte and Status Byte), to the initiator.

# **OPERATION CODES**

The first byte of the Command Descriptor Block contains the Operation Code of the SCSI command. The Operation Code has two parts as shown below, firstly the Group Code and secondly the Command Code. The Group Code is a three bit code, therefore there are eight command groups. The Command Code is a five bit code, therefore there are thirty-two commands within each group. This gives a total of 256 available command operation codes.

#### **Operation Code Command Descriptor Block**

| Bit    | 7          | 6 | 5 | 4 | 3  | 2       | 1   | 0 |

|--------|------------|---|---|---|----|---------|-----|---|

| Byte 0 | Group Code |   |   |   | Co | mmand C | ode |   |

Group Code

| 6 Byte Commands                 |

|---------------------------------|

| 10 Byte Commands                |

| Reserved                        |

| Reserved                        |

| Reserved                        |

| 12 Byte Commands                |

| Vendor Unique                   |

| Vendor Unique (6 Byte Commands) |

|                                 |

Of the eight possible command groups, only group 0, group 1 and group 7 are supported by the RO652. Only the Command Codes implemented by the RO652 are discussed. See ANSI specification X3T9 and common command set book for full description of all of the commands available.

### **Command Codes**

|         | Hexadecimal<br>Operation Code                                  | Command Name                                                                                                                                           |

|---------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Group 0 | 00<br>03<br>04<br>07<br>08<br>0A<br>0B<br>12<br>15<br>1A<br>1D | Test Unit Ready<br>Request Sense<br>Format Unit<br>Reassign Blocks<br>Read<br>Write<br>Seek<br>Inquiry<br>Mode Select<br>Mode Sense<br>Send Diagnostic |

| Group 1 | 25<br>28<br>2A<br>2F<br>37<br>3C<br>3B                         | Read Capacity<br>Read Extended<br>Write Extended<br>Verify<br>Read Defect Data<br>Read Data Buffer<br>Write Data Buffer                                |

| Group 7 | E0<br>E1<br>E2<br>E8<br>EA                                     | Maintenance Seek<br>Format Maintenance Tracks<br>Certify<br>Fast Read<br>Fast Write                                                                    |

# COMMAND DESCRIPTOR BLOCKS FORMAT

The number of bytes contained by the Command Descriptor Block (CDB) is dependent on the group of the command. Group 0 and Group 7 commands have a 6 byte CDB and Group 1 commands have 10 byte CDB. The Command Descriptor Block has an Operation Code as the first byte, as shown above, followed by a Logical Unit Number (LUN), command parameters (if any) and a Control Byte. If there is an invalid parameter in the CDB, the target will stop executing the command without altering the medium. Regardless of command completion, the target will return a status byte and a message byte to the initiator. The RO652 only supports Status Byte 02H (Check Condition) and Message Byte 00H (command complete), see ANSI spec for full description of other status and message bytes. Tables 3.1 and 3.2 show the typical command descriptor blocks for 6 and 10 byte commands. Tables 3.3 and 3.4 show the status and message byte command descriptor blocks.

| Bit    | 7     | 6                                   | 5         | 4                                          | 3         | 2          | 1  | 0 |  |  |

|--------|-------|-------------------------------------|-----------|--------------------------------------------|-----------|------------|----|---|--|--|

| Byte 0 |       | Operation Code                      |           |                                            |           |            |    |   |  |  |

| Byte 1 | Logic | al Unit N                           | lumber    | Logical Block Address MSB<br>(if required) |           |            |    |   |  |  |

| Byte 2 |       | Logical Block Address (if required) |           |                                            |           |            |    |   |  |  |

| Byte 3 |       | L                                   | ogical Bl | ock Addr                                   | ess LSB ( | if require | d) |   |  |  |

| Byte 4 |       | Transfer Length (if required)       |           |                                            |           |            |    |   |  |  |

| Byte 5 |       | Control Byte                        |           |                                            |           |            |    |   |  |  |

Table 3.1 : Typical 6 Byte Command Descriptor Block (Group 0 and Group 7)

Table 3.2 : Typical 10 Byte Command Descriptor Block (Group 1)

| Bit    | 7     | 6                                       | 5          | 4         | 3       | 2           | 1  | 0      |  |  |  |

|--------|-------|-----------------------------------------|------------|-----------|---------|-------------|----|--------|--|--|--|

| Byte 0 |       | Operation Code                          |            |           |         |             |    |        |  |  |  |

| Byte 1 | Logic | al Unit N                               | umber      |           | Res     | erved       |    | RelAdr |  |  |  |

| Byte 2 |       | Logical Block Address MSB (if required) |            |           |         |             |    |        |  |  |  |

| Byte 3 |       | Logical Block Address (if required)     |            |           |         |             |    |        |  |  |  |

| Byte 4 |       | Logical Block Address (if required)     |            |           |         |             |    |        |  |  |  |

| Byte 5 |       | L                                       | ogical Blo | ock Addre | ess LSB | (if require | d) |        |  |  |  |

| Byte 6 |       | Reserved                                |            |           |         |             |    |        |  |  |  |

| Byte 7 |       | Transfer Length MSB (if required)       |            |           |         |             |    |        |  |  |  |

| Byte 8 |       | Transfer Length LSB (if required)       |            |           |         |             |    |        |  |  |  |

| Byte 9 |       | Control Byte                            |            |           |         |             |    |        |  |  |  |

Logical Unit Number

The LUN addresses one of eight devices attached to the target.

Logical Block Address

The logical block address on logical units begins with block 0 and is contigous up to the last logical block on the unit. The logical block concept implies that the initiator and target have previously established the number of data bytes per logical block. This can be done using the Read Capacity command or the Mode Sense command. Group 0 and Group 7 Command Descriptor Blocks have a 21-bit logical block address. Group 1 Command Descriptor Blocks have a 32-bit logical block address.

| Relative Address (Rel<br>Adr) | The relative address of Group 1 Command Descriptor Blocks is<br>set to one to indicate that the logical block address is a two's<br>complement displacement. This negative/positive displacement is<br>added to the logical block address last accessed on the unit to<br>form the logical block address for that command. This is only<br>used when linking commands and is not supported by the RO652. |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transfer Length               | The transfer length specifies the amount of data to be transferred, usually the number of blocks.                                                                                                                                                                                                                                                                                                        |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                          |

Control Byte The control byte is the very last byte of every Command Descriptor Block. A typical Control Byte is shown below. For the R0652 Hard disk drive, all bits of the Control Byte are set to zero.

#### **Control Byte**

| Bit | 7      | 6      | 5 | 4    | 3    | 2 | 1    | 0    |

|-----|--------|--------|---|------|------|---|------|------|

|     | Vendor | Unique |   | Rese | rved |   | Flag | Link |

- Link Bit If the Link Bit is set to one the initiator wants an automatic link to the next command when the current command is successfully completed. This is not implemented in the RO652.

- Flag Bit If the Link Bit is set to zero, then the Flag Bit is set to zero. If the Link Bit is set to one and the command is successfully completed, the target sends a linked command complete message (if Flag Bit=0) or a linked command complete message with flag (if Flag Bit=1). This bit is typically used to cause an interrupt in the initiator between linked commands.

# STATUS

The status returned on completion of a command contains a Status Byte and a Message Byte.

Only the status supported by the RO652 is discussed here.

#### Table 3.3 : Status Byte

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

|--------|---|---|---|---|---|---|-----|---|

| Byte 0 | 0 | 0 | 0 | 0 | 0 | 0 | ERR | 0 |

ERR=0 no error occurred during command execution. ERR=1 error occurred during command execution. Most error conditions cannot be explained with a single status code and a Request Sense Command should be issued when ERR=1 to determine nature of the error.

Table 3.4 : Message Byte

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---|---|---|---|---|---|---|---|

| Byte 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

00H Command Complete is the only message supported by the RO652. This message is sent from a target to an initiator to indicate that the execution of a command has terminated and that a valid status has been sent to the initiator. This does not indicate correct or incorrect execution of the command. After this message is sent a Bus Free Phase is entered.

### **CHAPTER 4**

# ADVANTAGES OF SMALL COMPUTER SYSTEM INTERFACE (SCSI)

Before the SCSI bus standard emerged there were many different types of devices, most with different interfaces, which would typically be connected to a computer system. For example, a Winchester disk drive would have an ST506 interface, a tape streamer would have a QIC36 interface and a printer would have an RS232 interface. Therefore, it was necessary to have a different hardware controller for each of these devices. Although each of these were already industry standard interfaces, the introduction of SCSI as the new industry standard meant that the Winchester disk drive, the tape streamer and the printer would all have the same interface and could be controlled by the same hardware.

SCSI has a common command set, which allows the loading to be taken off the host system CPU as more tasks are performed by the SCSI controller. For example, Copy is a function of the common command set which allows transfer of data from one device in the system to another without host CPU monitoring. The common command set supports present and future peripherals, so new software drivers do not need to be written for upgraded devices. This makes system design independent of advances in device capacity and performance. Although the same SCSI hardware is able to control printers, hard disk drives, floppy disk drives etc. a different software driver is needed for each of them. The software has to take into account whether the connected device is a block device (eg. a hard disk drive) or a character device (eg. a printer).

SCSI also supports arbitration between connected devices, allowing several tasks from different devices to be interleaved on the bus at the same time as shown in Chapter 3.

# 4.1 ADVANTAGES FOR HARD DISKS

SCSI supersedes the ST506 interface as the new industry standard for hard disk drives and is supported by most major device manufacturers. The SCSI common command set ensures