## PARALLEL FUNCTIONAL PROGRAMMING FOR MESSAGE-PASSING MULTIPROCESSORS

## **Gerald Ostheimer**

## A Thesis Submitted for the Degree of PhD at the University of St Andrews

1993

Full metadata for this item is available in St Andrews Research Repository at:

http://research-repository.st-andrews.ac.uk/

Please use this identifier to cite or link to this item: http://hdl.handle.net/10023/13426

This item is protected by original copyright

# Parallel Functional Programming for Message-Passing Multiprocessors

Thesis submitted for the degree of Doctor of Philosophy at the

University of St. Andrews

by

Gerald Ostheimer

Division of Computational Science

Department of Mathematical and Computational Sciences

University of St. Andrews

St. Andrews, Fife, KY16 9SS

March 1993

ProQuest Number: 10167176

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10167176

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC.

789 East Eisenhower Parkway

P.O. Box 1346

Ann Arbor, MI 48106 – 1346

IN 8352

#### Declaration

I, Gerald Kuno Ostheimer, hereby certify that this thesis has been composed by myself, that it is a record of my own work, and that it has not been accepted in partial or complete fulfilment of any other degree or professional qualification.

I was admitted to the Faculty of Science of the University of St. Andrews under Ordinance General No 12 on 1st October, 1988 and as a candidate for the degree of Ph.D. on 1st October, 1989

I hereby certify that the candidate has fulfilled the conditions of the Resolution and Regulations appropriate to the Degree of Ph.D.

Date

$$31/3/93$$

# Copyright

In submitting this thesis to the University of St.Andrews I understand that I am giving permission for it to be made available for use in accordance with the regulations of the University Library for the time being in force, subject to any copyright vested in the work not being affected thereby. I also understand that the title and abstract will be published, and that a copy of the work may be made and supplied to any bona fide library or research worker.

#### Abstract

We propose a framework for the evaluation of implicitly parallel functional programs on message passing multiprocessors with special emphasis on the issue of load bounding. The model is based on a new encoding of the  $\lambda$ -calculus in Milner's  $\pi$ -calculus and combines lazy evaluation and eager (parallel) evaluation in the same framework. The  $\pi$ -calculus encoding serves as the specification of a more concrete compilation scheme mapping a simple functional language into a message passing, parallel program. We show how and under which conditions we can guarantee successful load bounding based on this compilation scheme. Finally we discuss the architectural requirements for a machine to support our model efficiently and we present a simple RISC-style processor architecture which meets those criteria.

## Acknowledgments

Many people have had profound influence on this thesis and I want to pay tribute to some of them here.

- To my supervisor, Tony Davie, for his willingness to supervise what started out as a thesis on computer architecture, for always being available for a quick word, and for giving me the freedom to follow my own way, however twisted.

- To Peter Burgess, for putting up with my quirks during two years of sharing an office, for sharing his experience on distributed systems, for his willingness to listen to half-baked ideas and for talking me out of the more silly ones.

- To Ron Morrison, for his encouragement of my work when he could see it taking shape.

- To Arvind, for instilling in me a fascination with non-strictness and parallel architectures.

- To David Gifford, for introducing me to the beauty of functional programming, and for demonstrating that lectures can be at once fun and challenge.

- To John Glauert, for pointing out the  $\pi$ -calculus to me at just the right moment.

- To Bill Campbell, for guiding my life's journey to the beautiful town of St. Andrews.

- To Kathy Hargreaves, whose competent editing advice on my MSc thesis helped me no end with this larger undertaking.

- To my many friends, whose confidence in me always seemed greater than my own.

- Finally, to my parents for their unquestioning love and support, and especially to my father, for his living example of the spirit behind that old saying, "a job worth doing is a job worth doing well."

# **Table of Contents**

| Chapter 1 — | - Introduction                                                  |                                                                |    |  |

|-------------|-----------------------------------------------------------------|----------------------------------------------------------------|----|--|

| 1.1         | Parallel computing and functional programming                   |                                                                |    |  |

| 1.2         | Contribution of this thesis                                     |                                                                |    |  |

| 1.3         | Why functional programming matters                              |                                                                |    |  |

| 1.4         | What is holding us back?                                        |                                                                |    |  |

| 1.5         | 'Functional' architectures                                      |                                                                |    |  |

| 1.6         | Current work                                                    |                                                                |    |  |

| 1.7         | Where we fit in                                                 |                                                                |    |  |

|             | 1.7.1                                                           | Concurrency in functional programming                          |    |  |

|             |                                                                 | systems and the $\pi$ -calculus                                | 11 |  |

|             | 1.7.2                                                           | Automatic load bounding                                        | 13 |  |

|             | 1.7.3                                                           | Granularity                                                    | 15 |  |

| 1.8         | Thesis                                                          | outline                                                        | 16 |  |

| Chapter 2 — | - Previo                                                        | us and Related Work                                            | 18 |  |

| 2.1         | Conter                                                          | nts                                                            | 18 |  |

| 2.2         | Functional processes: simulating the $\lambda$ -calculus in the |                                                                |    |  |

|             | π-calculus                                                      |                                                                |    |  |

|             | 2.2.1                                                           | The $\pi$ -calculus: a simple example                          | 19 |  |

|             | 2.2.2                                                           | The $\pi$ -calculus: syntax and reduction behaviour            | 20 |  |

|             | 2.2.3                                                           | A comparison of the $\pi$ -calculus to the $\lambda$ -calculus | 22 |  |

|             | 2.2.4                                                           | Simulating the normal-order λ-calculus                         | 23 |  |

|             | 2.2.5                                                           | Simulating the call-by-value λ-calculus                        | 26 |  |

| 2.3         | The Manchester dataflow project                                 |                                                                |    |  |

|             | 2.3.1                                                           | Architectural overview                                         | 29 |  |

|             | 2.3.2                                                           | Load bounding in the Manchester dataflow                       |    |  |

|             |                                                                 | machine                                                        | 31 |  |

| 2.4         | The MIT dataflow project                                        |                                                                |    |  |

|             | 2.4.1                                                           | From static dataflow to Monsoon                                | 32 |  |

|             | 2.4.2                                                           | Dataflow/von Neumann hybrid processors                         | 35 |  |

|             | 2.4.3                                                           | Load bounding for the MIT dataflow machines                    | 39 |  |

| 2.5         | ALICE                                                           | /Flagship                                                      | 40 |  |

| 2.6         | GRIP                                                            |                                                                |    |  |

| 2.7         | Lazy Task Creation                                              |                                                                |    |  |

| 2.8         | Other previous work 4                                           |                                                                |    |  |

| Chapter 3 — | - A Sim                                                         | ulation of the $\lambda$ -Calculus in the $\pi$ -Calculus      | 45 |  |

| 3.1         | Contents                           | 45 |  |

|-------------|------------------------------------|----|--|

| 3.2         | Motivation                         |    |  |

| 3.3         | Overview                           | 46 |  |

|             | Protocol 1 (Variables)             | 47 |  |

|             | Protocol 2 (Abstractions)          | 47 |  |

| 3.4         | The translation scheme             |    |  |

|             | 3.4.1 Environment entry            | 48 |  |

|             | 3.4.2 Name reference               | 49 |  |

|             | 3.4.3 Abstraction                  | 49 |  |

|             | 3.4.4 Eager application            | 50 |  |

|             | 3.4.5 Lazy application             | 50 |  |

| 3.5         | Sample reductions                  |    |  |

|             | 3.5.1 Simple function application  | 52 |  |

|             | 3.5.2 Sharing of computation (1)   | 53 |  |

|             | 3.5.3 Sharing of computation (2)   | 55 |  |

| 3.6         | Discussion                         | 57 |  |

| Chapter 4 - | - A Practical Compilation Scheme   | 58 |  |

| 4.1         | Introduction                       | 58 |  |

| 4.2         | Source language                    | 59 |  |

| 4.3         | Architectural framework            | 60 |  |

| 4.4         | Runtime framework                  | 61 |  |

| 4.5         | Overview of the compilation scheme | 63 |  |

| 4.6         | Translating non-strict expressions |    |  |

|             | 4.6.1 Constants                    | 66 |  |

|             | 4.6.2 Identifier reference         | 67 |  |

|             | 4.6.3 Lazy function application    | 68 |  |

|             | 4.6.4 Lazy let                     | 69 |  |

|             | 4.6.5 Lazy cons                    | 69 |  |

|             | 4.6.6 Conditional                  | 70 |  |

| 4.7         | Translating strict expressions     |    |  |

|             | 4.7.1 Eager function application   | 71 |  |

|             | 4.7.2 Eager let                    | 72 |  |

|             | 4.7.3 Eager cons                   | 73 |  |

|             | 4.7.4 Addition                     | 74 |  |

| 4.8         | Summary                            | 75 |  |

| Chapter 5 — | - Load Bounding                    | 76 |  |

| 5.1         | Introduction                       |    |  |

| 5.2         | Pitfalls and dangers               | 76 |  |

|             |                                    |    |  |

| 5.3         | A workable solution 7                             |                                              |     |  |

|-------------|---------------------------------------------------|----------------------------------------------|-----|--|

| 5.4         | Eager                                             | compilation rules modified for load bounding | 80  |  |

|             | 5.4.1                                             | Eager function application                   | 80  |  |

|             | 5.4.2                                             | Eager let                                    | 82  |  |

|             | 5.4.3                                             | Eager cons                                   | 83  |  |

|             | 5.4.4                                             | Eager addition                               | 84  |  |

| 5.5         | Adapti                                            | ng to changes in the workload                | 85  |  |

| 5.6         | Efficient load computation and load testing       |                                              |     |  |

|             | 5.6.1                                             | Probabilistic load estimation                | 87  |  |

|             | 5.6.2                                             | Cyclic load determination                    | 87  |  |

|             | 5.6.3                                             | A hybrid solution and its cost               | 89  |  |

| 5.7         | The pr                                            | oblem of sharing                             | 90  |  |

| 5.8         | Summ                                              | ary                                          | 92  |  |

| Chapter 6 — | The S7                                            | FAR:DUST Architecture                        | 93  |  |

| 6.1         | Introduction                                      |                                              |     |  |

| 6.2         | Architectural requirements for scalable, parallel |                                              |     |  |

|             | programs                                          |                                              |     |  |

|             | 6.2.1                                             | Scalability                                  | 94  |  |

|             | 6.2.2                                             | Topology independence                        | 95  |  |

|             | 6.2.3                                             | Asynchronous, message passing                |     |  |

|             |                                                   | communications                               | 95  |  |

|             | 6.2.4                                             | Fast context switching and process           |     |  |

|             |                                                   | synchronisation                              | 96  |  |

|             | 6.2.5                                             | Sequential efficiency                        | 96  |  |

| 6.3         | STAR:DUST as a RISC processor                     |                                              | 96  |  |

| 6.4         | STAR:DUST as a building block for multiprocessor  |                                              |     |  |

|             | systems                                           |                                              |     |  |

| 6.5         | Discussion                                        |                                              |     |  |

|             | 6.5.1                                             | Is STAR:DUST still a RISC architecture?      | 99  |  |

|             | 6.5.2                                             | Does STAR:DUST require infinite buffers?     | 99  |  |

|             | 6.5.3                                             | What network bandwidth can we reasonably     |     |  |

|             |                                                   | assume?                                      | 100 |  |

| 6.6         | Sample                                            | Programs                                     | 100 |  |

| 6.7         | Origin                                            | s of the STAR:DUST Architecture              | 103 |  |

| 6.8         | Summary                                           |                                              |     |  |

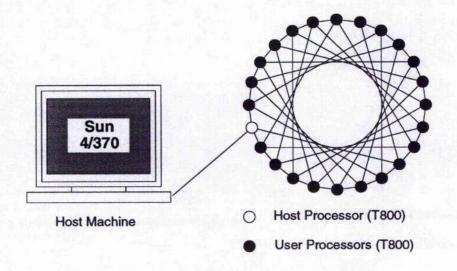

| Chapter 7 — |                                                   | outed Implementation of a STAR:DUST Emulator | 105 |  |

| 7.1         | Introduction                                      |                                              |     |  |

| 7.2         |                                                   | eiko Computing Surface and CSTools           | 105 |  |

| 7.3         | System structure, routing and deadlock avoidance           |     |  |

|-------------|------------------------------------------------------------|-----|--|

| 7.4         | Node structure                                             | 109 |  |

| 7.5         | Experimental results                                       | 111 |  |

| 7.6         | Summary                                                    |     |  |

| Chapter 8 — | - Conclusion                                               | 115 |  |

| 8.1         | What we have accomplished                                  | 115 |  |

| 8.2         | Specifying parallel graph reduction in the $\pi$ -calculus | 115 |  |

| 8.3         | Compilation scheme                                         | 116 |  |

| 8.4         | Load bounding and runtime system                           | 117 |  |

| 8.5         | The STAR:DUST machine                                      | 119 |  |

| 8.6         | Implementation and experimentation                         | 120 |  |

| 8.7         | Epilogue                                                   | 120 |  |

| Bibliograph | v                                                          | 122 |  |

## Chapter 1 — Introduction

## 1.1 Parallel computing and functional programming

Fifteen years after John Backus' clarion call to break the von Neumann bottleneck by adopting a functional programming style [Ba78], commercial multiprocessors are now available whose degree of parallelism is limited only by the size of a customer's wallet. Yet, there is little agreement on how best to program those machines and functional programming is not even among the leading contenders. While real speedups have been achieved for parallel functional programs on shared-memory multiprocessors with a limited degree of parallelism [AJ89], an effective scalably parallel solution is still outstanding. We hope that the work presented here will be an important step towards the goal of scalable parallel functional computing. We begin this introductory chapter by summarising our main results. We then state our perspective of the role and the historical development of parallel functional computing and show how our work ties in with previous developments. We conclude the chapter with a 'road map' to the rest of the thesis.

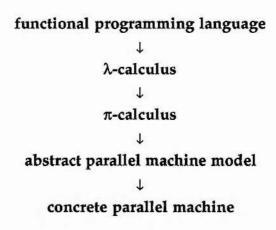

#### 1.2 Contribution of this thesis

Central to this thesis is a framework for the evaluation of implicitly parallel functional programs on message-passing multicomputers. Our model is based on a new encoding of the  $\lambda$ -calculus in Milner's  $\pi$ -calculus. Milner has given two such encodings in [Mi92], a sequential one with call-by-name parameter passing semantics and a parallel one with call-by-value parameter passing semantics. Ours combines the advantages of both in the same framework. We can choose individually for each function application between eager and lazy evaluation based on the results of strictness analysis.

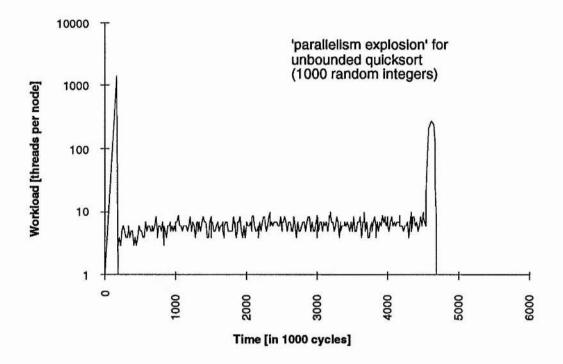

We are thus able to preserve non-strict semantics and at the same time exploit parallelism where safely possible. Our  $\pi$ -calculus encoding serves as the specification of a more concrete compilation scheme mapping a simple functional language into a message passing, parallel program by exploiting the implicit parallelism of functional programs. Since implicit parallelism gives rise to the problem of the parallelism explosion we give special emphasis to the issue of automatic load bounding. Without load bounding, the space requirements of some programs can change from linear to exponential. Our simple adaptive algorithm is integrated into the compilation scheme. We give an informal proof for the effectiveness of this algorithm, based on the structure of the compilation scheme, and discuss the limitations of our method. We discuss the architectural requirements for a machine to support our model efficiently and present the STAR:DUST architecture, short for 'St. Andrews RISC: Dataflow Using Sequential Threads', designed to meet those criteria. A STAR:DUST node is a simple RISC processor with two new instructions supporting message passing and task switching. We have simulated a multiprocessor STAR:DUST machine on a Meiko Computing Surface and have obtained experimental results based on this simulator.

## 1.3 Why functional programming matters

The virtues of programming in a functional style have been addressed often and eloquently enough for us not to dwell too long on this subject. In short, functional languages lend themselves to a declarative style of programming, often permitting a literal translation of a mathematical specification into a functional program. Many algorithms can be expressed in a succinct and intuitive manner unmatched by the prevalent imperative languages (see Hughes [Hu89]). This is due mostly to non-strict semantics which guarantees the termination of a larger class of programs. There is an

'algebra of functional programs' in the sense of Backus [Ba78] with a range of correctness-preserving transformations that facilitates correctness proofs and the derivation of efficient programs from specifications. The interested reader is referred to work by Darlington [Da82] and Bird [Bi89] for a more comprehensive exposition of these features. Of special interest for our work is the fact that functional languages do not force the programmer to impose a total order on program execution. Referential transparency ensures that only data dependencies constrain the order of evaluation. The resulting freedom can be exploited by systems like ours to extract parallelism from programs not necessarily written with parallel execution in mind. This is not to say, however, that writing parallel functional programs is a trivial task. While a compiler can easily extract parallelism from a particular functional program, different algorithms for the same problem may exhibit different amounts of parallelism, so good parallel programs will still require a special effort on the part of the programmer.

## 1.4 What is holding us back?

Only in relatively few cases—certainly when compared to the size of the present-day software industry—has functional programming had any impact on the practical solution of real world problems. This fact can not just be blamed on the inertia of practitioners who haven't been exposed to functional programming during the course of their training. Functional programming languages have long been suffering from a number of deficiencies. Chief among them is the difficulty of expressing non-trivial forms of I/O and, more generally, expressing many algorithms that are intuitively based on the notion of state. The nondeterminism of functional languages with respect to execution order, which is so beneficial to us for the purpose of parallelisation, also has its downside. Visualising the evaluation of a non-trivial functional program under a lazy or a parallel execution

regime is exceedingly hard. Convential debugging techniques fail. In particular, the notion of 'stepping through a program' has little meaning in a functional context. For similar reasons, classical complexity analysis does not readily apply to functional programs. Finally, despite impressive progress that has been made with 'compiled graph reduction' originating with Johnsson [Jo84], functional programming systems are still behind their imperative cousins in terms of efficiency when measured on real-world algorithms. We will not enter into a discussion of the various reasons for this handicap. Let it suffice to say that one of the requirements for the design of Fortran, generally considered to be the first 'high-level' programming language, was to map to machine languages with minimal loss of efficiency. Recently this close relationship has been reinforced with the design of RISC microprocessors as 'C' machines, as described by Patterson and Sequin in [PS81].

#### 1.5 'Functional' architectures

Since the earliest days of functional programming languages, their potential for parallelism has been recognised [Bu75]. At times, their inherent parallelism was presented as a means to catch up with imperative languages in the benchmark race. This expectation is, of course, to be taken with a large grain of salt. The competition for a parallel functional program is a parallel imperative one, thus moving the goalposts. However, there is some hope that parallel functional programming will indeed one day gather a larger following. The primary reason for this expectation is the enormous complexity of any but the most simple-minded imperative models for parallel programming. Reasoning about the correctness of a message-passing program, i.e., comprehending it, involves demonstrating its freedom of deadlock and starvation. See, for example Brookes and Roscoe [BR91]. Non-determinism is also a serious problem, especially when it

comes to debugging. Functional programs, on the other hand, are deterministic by definition and have no need for special new 'parallel constructs' which could affect correctness.

Most of the initial work on parallel functional programming centered around various proposals for computer architectures specially designed to support functional programming, e.g., the FFP machine [Ma79], the Manchester dataflow machine [GW78], the MIT tagged token data flow machine [AK80] and ALICE [DR81]. A comprehensive survey can be found in [Ve84]. The reason for this focus on computer architecture was twofold. In the first place there simply were no parallel architectures available commercially at the time. The first research multiprocessor, the Illiac IV had only become fully operational in 1975 [Fa76], while the first commercial multiprocessor built according to scalable design principles, the Denelcor HEP, did not arrive until 1981 [Sm81, HB84]. But there was a second reason. Since imperative languages were seen as being wedded to von Neumann machines, the search was on for a 'non-von Neumann' machine which would execute functional programs in a kind of 'native mode'. With the benefit of hindsight, this search can safely be said to have failed. While some of the architectural projects did produce very interesting results (among them the hardware mechanism for load bounding by Ruggiero and Sargeant [RS87] inspiring our software solution, see Chapter 2), few of the proposed architectures were constructed and none of them was commercially successful. To our knowledge only the MIT project is still continuing as an architectural effort after undergoing a major transformation back towards a modified von Neumann model (see below). Several factors contributed to thwart the early hopes for 'functional architectures'. Principal among them is the problem of excessively fine granularity. The necessary overhead for managing and synchronizing a

large number of small tasks often dwarfed any benefit that could be obtained from parallelism. Secondly, mainstream computer architecture did not stand still. Speed improvements for sequential microprocessors have continued at an enormous rate even to the present day. High-bandwidth, low latency networks were developed for connecting large numbers of conventional von Neumann microprocessors [DS87, Le92]. Interface technology has been advanced tying processors closely to networks, e.g., for the transputer [Wh85], the J-Machine [DC89], the CM-5 [Le92]. See also [HJ92] for a recent proposal. Finally, it has now been recognized that economies of scale will favour, for the forseeable future, parallel machines made out of large numbers of cheap von Neumann style microprocessors over special-purpose parallel processor designs.

#### 1.6 Current work

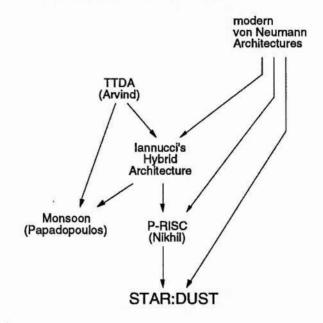

Work on parallel functional programming has not stopped, however. Current activities can be broadly divided into two classes. On the architectural side efforts have been directed towards a rapprochement with von Neumann microprocessor technology. In the case of the MIT dataflow project this was a gradual process: from the fine-grain, tagged-token dataflow architecture Monsoon [PC90], via Iannucci's hybrid architecture [Ia88] and P-RISC [AN88], the MIT work has now progressed to the design of a coprocessor for the Motorola 88100, the \*T (pronounced 'Start') project [NP92]. The GRIP project [PC87] at Glasgow ('Graph Reduction in Parallel') has been designed from the outset around a commercial microprocessor, the Motorola 68020.

The bulk of ongoing work, however, now concentrates its efforts on attempts to support the various forms of parallel architectures that have been developed for different programming models. Shared-memory machines are the target of work that has been done at Chalmers by Augustsson and Johnsson [AJ89]. The FAST project at Imperial College and Southampton [GH90] supports networks of communicating processes such as those constructed with transputers. Hudak and his colleagues have implemented parallel graph reduction on an Intel hypercube as part of their work on the Alfalfa project [GH87]. Work by Cole at Glasgow [Co90] and Darlington at Imperial College on algorithmic skeletons is somewhat broader in scope. They propose writing parallel functional programs in terms of generic functions which would be implemented efficiently on a host of different architectures, spanning parallel models from SIMD to MIMD. For all their diversity, these projects share certain characteristics. In order to take advantage of parallelism, programmers need to use annotations of some sort to specify where parallelism is to be obtained. Consequently programmers are also responsible for bounding parallelism to sustainable levels. Furthermore, only coarse-grain parallelism can typically be exploited with any efficiency. The resulting programs often become nonportable and non-scalable. We will discuss some of these projects in more detail in Chapter 2.

#### 1.7 Where we fit in

Our fundamental interest is in implicit parallelism for scalable computers. In this section we will state the problems we set out to address and discuss the motivations behind our research. We will indicate how those motivations arose from previous work in the field.

## 1.7.1 Concurrency in functional programming systems and the $\pi$ -calculus

David Turner's popularisation of combinators [Tu79] provided the functional programming community with a beautiful theory for defining the semantics of program execution in terms of combinator reduction. At the same time his work resulted in an implementation technique which

has since been refined to compiled graph reduction, now universally considered the most efficient method of evaluating functional programs on off-the-shelf sequential machines. Many researchers have now undertaken to apply the basic model of graph reduction to parallel evaluation as well. This is possible since the graph reduction model preserves the parallelism implicit in functional languages. Obviously the implicit parallelism needs be made explicit at some stage, either during compilation or during evaluation. This is typically done in an ad-hoc manner suitable to the kind of parallel machine supported by a particular project. It is our contention that it is both useful and possible to elevate the process of 'making parallelism explicit' to a higher level in the design of a parallel functional language system. What is needed is a proper theory of concurrency in parallel functional programming. In the  $\pi$ -calculus [Mi92] Robin Milner provides us with the necessary tools for such a theory, demonstrated by his two encodings of the  $\lambda$ -calculus in the  $\pi$ -calculus. We extend his work to modelling a functional programming system which exploits parallelism and preserves non-strictness, taking up a theme from [Mi92].

Thus, strategies which appear natural in the presence of textual substitution may not seem so natural in a model involving autonomous agents. The former have clearly been most deeply studied in research on the  $\lambda$ -calculus; one effect of providing  $\pi$ -calculus as a substrate may be to intensify the study of other strategies, such as those with shared reductions. (Emphasis ours)

We would like to note that we approached the problem strictly from an implementation point of view and have been made aware of the  $\pi$ -calculus only at a late stage of the work described here. In particular, our compilation scheme for message-passing multicomputers predates our  $\pi$ -calculus

encoding for the  $\lambda$ -calculus which is best viewed as a crystallisation of the main ideas.

#### 1.7.2 Automatic load bounding

Consider the 'nfib' program, a program so trivial that it is now almost considered bad taste to publish performance figures based on it:

```

nfib 0 = 1

nfib 1 = 1

nfib n = 1 + nfib (n-1) + nfib (n-2)

```

'nfib' is strict throughout, contains neither fancy data structures nor higher order functions and offers vast amounts of parallelism of a very simple kind. Any functional implementation, so the reasoning goes, should do well on it. Yet in the context of implicit parallelism 'nfib' poses a difficult problem. Sequential execution of 'nfib' corresponds to a depth-first traversal of the tree-structured program graph. Therefore sequential 'nfib' requires space proportional to the maximum depth of recursion, i.e., it runs in linear space. Maximally parallel evaluation of 'nfib', however, corresponds to breadth first traversal and worst case space requirements are proportional to the size of the program graph, i.e., we now require exponential space. Even relatively small instances of parallel 'nfib' can exceed machine resources. At the same time we obtain no benefit from exploiting parallelism far in excess of the hardware parallelism at our disposal. So clearly we are interested in bounding the amount of parallelism we will uncover. This problem was anticipated by Burton and Sleep in [BS81] where the basic idea for an adaptive solution is also outlined: follow a breadth-first evaluation strategy while the machine is underloaded, perform depth-first evaluation while the machine is saturated.

The 'parallelism explosion' was observed experimentally in the dataflow community and reported in [RS87, CA88]. Our work is closely related to that of Ruggiero and Sargeant who have implemented a hardware load *throttle* as part of their work on the Manchester dataflow machine. We are picking up an idea proposed in [RS87]

Another idea for dynamic software throttling is to plant two types of code for any parallel program: one serial and the other parallel. The machine switches from one style of code to the other at run time, according to how busy it is.

#### However, they go on to add

Although this method could be useful in the future, achieving a complete solution in this way is well beyond the state of the art. The conclusion is that despite being useful, software techniques are not enough to implement a general and effective throttle. We need some help from the hardware.

In this paper we present a software only solution with little overhead—in particular, we do not require expensive scheduling hardware. In addition, our work is novel in the following ways:

- We integrate our load bounding method into a simple compilation scheme for lazy functional languages.

- We present an informal proof of the effectiveness of our scheme based on the structure of the generated code.

- · We identify sharing as a possible source of problems for load bounding.

## 1.7.3 Granularity

Consider the following simple functional program

let

$$x = a*b;$$

$y = 4*c$

in  $(x+y) * (x-y)$

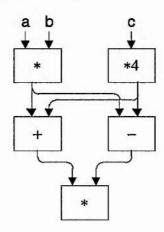

and its dataflow graph (Figure 1.1). This example has been taken (in slightly simplified form) from [AC86] where it is used to demonstrate the instruction level parallelism implicit in many functional programs (or dataflow programs). In the example, x and y can be computed concurrently, and so can the addition and the subtraction.

Figure 1.1: Instruction level parallelism

The original dataflow machine designs attempted to exploit instruction-level parallelism of this form as a special case of the general method. Experience with completed dataflow hardware has demonstrated, however, that the overheads of dispatching tiny parcels of work and synchronizing their results easily outweighs any benefits to be obtained from such parallelism. In fact, recent designs for superscalar (sequential) microprocessors have managed to exploit instruction-level parallelism much more effectively, see for example [DA92, MW92]. For this reason,

much of the recent work on parallel functional programming has focussed on restricting the exploitation of functional parallelism to the coarse-grain type.

Since the 'right' level of granularity depends largely on architectural parameters, it is hard to identify while parallel computer architecture is a quickly moving target. We consider the trend to coarse-grain parallelism within the functional community to be an overcompensation for the previous focus on excessively fine-grain parallelism. Our working hypothesis is that it will be possible to support parallelism efficiently on the inter-function level (we do not attempt to exploit parallelism within function bodies). The trend towards closer integration of network interfaces and high-bandwidth networks [EC92, HJ92] permits more efficient synchronisation than previously considered feasible. In Chapter 6 we present a model RISC architecture with a tightly integrated network interface [Os91]. STAR:DUST was heavily influenced by Nikhil's P-RISC architecture [AN88] described in the next chapter.

We restrict ourselves to distributed memory, message passing machines as those now appear set to prevail among massively parallel architectures. This trend is exemplified by the development history of the Connection Machine, originally a pioneering SIMD architecture, which was recently reborn in MIMD form [Le92].

#### 1.8 Thesis outline

In this chapter we have outlined the main contributions of this thesis and the developments which preceded and motivated our work. In Chapter 2 we will have a closer look at some previous work important to ours. Chapter 3 contains a simulation of the  $\lambda$ -calculus in Milner's  $\pi$ -calculus which serves as a specification for the compilation scheme presented in Chapters 4 and 5. The former contains the basic set of compilation rules

required for lazy functional programming with alternative 'eager' rules for exploiting parallelism where safely possible. In the latter we adapt the eager rules to tie in with an efficient distributed load bounding algorithm in order to limit the resource requirements of the resulting programs and we give an informal proof of the effectiveness of the resulting scheme. In Chapter 6 we detail our proposal for STAR:DUST, a model RISC architecture for fine-grain parallel computing. In Chapter 7 we describe our simulation of this architecture on a commercial multiprocessor and present some experimental results obtained from the simulator. We conclude in Chapter 8 with a brief summary and suggestions for further work.

## Chapter 2 — Previous and Related Work

#### 2.1 Contents

In this chapter we will give a summary of previous work of which we make use, previous work that we improve on, as well as current related work moving in different directions. Parallel functional programming is a large field and we necessarily have to restrict our attention to those contributions that we deem most relevant to our work. In outline, we will give some details about Milner's  $\pi$ -calculus as well as his encodings of the  $\lambda$ -calculus. We will discuss some aspects of the Manchester dataflow project, in particular their achievements on load bounding. We review the development of the MIT dataflow work and discuss the design of the P-RISC architecture that grew out of it. We include a section on the first parallel graph reduction machine, ALICE, and its successor, Flagship. We discuss the design of the GRIP architecture, a major project in parallel functional programming which includes a strong architectural component. We conclude with a comparison of our load bounding approach to that of 'lazy task creation'.

## 2.2 Functional processes: simulating the $\lambda$ -calculus in the $\pi$ -calculus

The  $\pi$ -calculus is the result of a search for a algebraic framework which would capture the essence of the notion of concurrent processes. It is particularly suitable for the description of systems which can change their configuration dynamically. The  $\pi$ -calculus improves on Milner's previous work on CCS, the *calculus of communicating systems* [Mi80], in that the former needs no recourse to a universe of values outside its own scope. In terms of internal completeness and conciseness it is comparable to the  $\lambda$ -calculus which was a guiding paradigm in the design of the  $\pi$ -calculus. See Milner's Turing Award Lecture [Mi93] for an excellent discussion of the

motivations that lead to the  $\pi$ -calculus. This section will be important to the rest of the thesis in two ways: we will require an understanding of the operational behaviour of the  $\pi$ -calculus in Chapter 3, where we use it to specify a non-strict parallel simulator for the  $\lambda$ -calculus. Secondly we will present a brief outline of two such simulations given by Milner in [Mi92], one of them non-strict but sequential, the other parallel but strict.

#### 2.2.1 The $\pi$ -calculus: a simple example

Rather than getting immediately bogged down in notation and detail, let us start by presenting a simple  $\pi$ -calculus term, the simplest term which admits reduction:

$$\bar{x}z \mid x(y)$$

This term is to be read as follows: write z to x and, in parallel, read y from x. Reduction is possible since there is a reader and a writer ready to communicate via the same channel, namely x. Communication takes place by cancelling read- and write-actions and substituting the value to be written (z in the example) for any free occurrence in the reading process of the variable to be read (y in the example). As y does not occur free anywhere, reduction yields

0 1 0

which is equivalent to 0, the empty process. A slightly more useful example is the term

$$\bar{x}z \mid x(y).\bar{x}y$$

Here the read-action x(y) is followed by a write-action  $\bar{x}y$ . Reduction yields

$0 \mid \bar{x}z$

after cancelling matching read/write-actions and substituting z for the single free occurrence of y.

#### 2.2.2 The $\pi$ -calculus: syntax and reduction behaviour

We are now ready for a more systematic presentation of the  $\pi$ -calculus, adhering to the form given in [Mi92]. The  $\pi$ -calculus consists of a set of terms which intuitively stand for *processes*. The names of the  $\pi$ -calculus (x, y, z...) denote *channels* through which processes communicate. Channel names are also the only *subject* of communication. The syntax for  $\pi$ -calculus terms is summarised in Figure 2.1.

::==  $\bar{x}y.P$ write-action: write y to x and then P x(y).Pread-action: read y from x and then P ::= 0 ::= empty process ::=  $P_1 \mid P_2$ composition (y) P restriction ::= 1P ::= replication

Figure 2.1: Syntax of the  $\pi$ -calculus

The terms of the  $\pi$ -calculus exhibit a simple block structure with two forms of name binding, namely read-action and restriction. In the following we will discuss each of the constructs in some more detail.

Write-action. A term of the form  $P = \bar{x}z.Q$  represents a synchronous send-operation of a value z along a channel x. The process P cannot proceed until another process is ready to receive z on the same channel and will then continue with Q.

Read-action. Counterpart to a write-action. A process of the form x(y).Q cannot proceed until another process is ready to send some value v along the channel x. The value v is then substituted for all free occurrences of y inside Q. The read-action is one of two ways of binding names, i.e., the scope of y is Q.

Empty process. We write  $\mathbf{0}$  to represent the empty process which is necessary to ground our syntactic rules. We will always abbreviate action terms of the form  $\bar{x}z.\mathbf{0}$  to  $\bar{x}z$  (similarly for read-actions).

Composition. We write  $P_1 \mid P_2$  to denote two processes  $P_1$  and  $P_2$  operating concurrently. Note that there is no separate construct for sequential composition. This can be modelled using parallel composition and suitable synchronisation via interaction.

Restriction. We write (x)P to obtain a new channel name x which is private to P. The term  $\overline{x}z \mid (x)x(y)$  has no reduction, as the sending process and the receiving process operate on different channels. Restriction is the second form of name binding, with P as the scope of x.

Replication. A term of the form !P stands for the parallel composition of as many instances of the term P 'as necessary'. Replication can be 'unwound' according to the structural equivalence ! $P \equiv P \mid !P$ . Unwinding is unnecessary when there are existing copies of P which have not participated in any interactions. Note that unwinding does not represent reduction but is a structural equivalence relation like, for example,  $\alpha$ -conversion.

In addition to these basic constructs we will also use a number of shorthands as defined below:

$$\overline{x}(y).P$$

$\stackrel{\mathrm{def}}{=}$   $(y)\,\overline{x}\,y.P$  write a new channel y to x  $x(y)(z).P$   $\stackrel{\mathrm{def}}{=}$   $x(y).x(z).P$  multiple reads from x  $\overline{x}\,yz.P$   $\stackrel{\mathrm{def}}{=}$   $\overline{x}\,y.\,\overline{x}\,z.P$  multiple writes to x

Note in the first rule how private names (y above) can be exported out of the scope of restriction via explicit communication. Note, finally, that all occurrences of (x) signify bindings for the channel name x with simple static scoping rules.

The basic reduction rule, already hinted at in our explanation of read- and write-actions, is the following: for a pair of processes

$$Q_1 = \overline{x} z.P_1$$

and  $Q_2 = x(y). P_2$

we get the reduction

$$Q_1 | Q_2 \rightarrow P_1 | P_2 \{z/y\}.$$

Put in words, if  $Q_1$  is ready to send a name z along the channel x and  $Q_2$  is ready to receive a name along the same channel then they can interact. Interaction results in cancelling each of the two send/receive actions and substituting z for all occurrences of y inside  $P_2$ . The complete set of reduction rules describes in detail the distribution of reduction over restriction and replication constructs, omitted here for sake of brevity. They can be found in [Mi92] along with a complete definition of structural equivalence for terms.

#### 2.2.3 A comparison of the $\pi$ -calculus to the $\lambda$ -calculus

It will be useful to compare the  $\pi$ -calculus with the  $\lambda$ -calculus both to gain further understanding of the  $\pi$ -calculus itself and to appreciate the task before us of simulating the latter with the former. At the most elementary level, both calculi are term rewriting systems with a simple basic reduction rule. Both have simple static scoping rules for names. Neither provides any computational 'sugar' but both of them are computationally complete (for the  $\pi$ -calculus this will follow from the fact that it can simulate the  $\lambda$ -calculus). In the  $\lambda$ -calculus, the basic concept is that of a function: terms represent functions and names denote functions. Functions are first-class objects. In the  $\pi$ -calculus, there are two basic entities, processes and channels. Terms represent processes, but processes are not first-class in that

the names of the  $\pi$ -calculus stand for channels only and channels are the only subject of of communication. There is a superficial correspondence between  $\beta$ -reduction in the  $\lambda$ -calculus and communication in the  $\pi$ -calculus in that both involve the substitution of an 'actual parameter' for a 'formal parameter'. However, while the term providing the actual parameter in a βreduction becomes merged with the abstraction term, both reader and writer processes engaging in a  $\pi$ -calculus communication continue as independent agents after interacting. Studying the two reduction mechanisms closely we observe that β-reduction is the more complex of the two, involving as it does terms as actual parameters rather than 'atomic' channel names. On the other hand, identifying a redex in the  $\lambda$ -calculus is a simple 'local' syntactic operation whereas reduction in the  $\pi$ -calculus involves identifying two matching redexes, a reader and a writer, which can occur anywhere within a term (see the example below). A final and fundamental difference between the two calculi is that normal forms for  $\lambda$ -calculus terms are unique, whereas the  $\pi$ -calculus is nondeterministic. Consider for example the two reductions

$$x(y) \mid \overline{x}z_1 \mid \overline{x}z_2 \rightarrow 0 \mid 0 \mid \overline{x}z_2 \equiv \overline{x}z_2$$

$x(y) \mid \overline{x}z_1 \mid \overline{x}z_2 \rightarrow 0 \mid \overline{x}z_1 \mid 0 \equiv \overline{x}z_1$

Each yields a different normal form, depending on which send-action succeeds.

## 2.2.4 Simulating the normal-order $\lambda$ -calculus

The motivation behind simulating the  $\lambda$ -calculus in the  $\pi$ -calculus is twofold. Firstly, it serves to demonstrates the power of the latter by relating it to its better-established cousin. Secondly, simulation of the  $\lambda$ -calculus is a useful application for the  $\pi$ -calculus, demonstrating its capability for expressing concurrency in  $\lambda$ -calculus reduction. In the first of two encodings

for  $\lambda$ -calculus reduction, Milner presents a scheme for the normal-order (sequential)  $\lambda$ -calculus in [Mi92] from which the following is largely quoted. Note that even without any explicit sequencing combinator, the  $\pi$ -calculus is capable of expressing sequentiality by suitable synchronisation.

Each  $\lambda$ -calculus term M is encoded as [[M]], a function which maps names to  $\pi$ -calculus terms. So [[M]] u is a term of the  $\pi$ -calculus with the intuition that the name u is the link along which [[M]] 'receives' its arguments. Now, suppose that M will itself be used in place of an argument represented by the variable x, i.e., x is bound to M. Each time M is 'called', via x, it must be told by the caller where to receive its own arguments. (In more familiar terminology, it must be given a *pointer* to its arguments). Thus the 'environment entry' binding x to M is a  $\pi$ -term defined as follows, with w representing the argument pointer(s).

$$[[x := M]] \stackrel{\text{def}}{=} !x(w). [[M]] w$$

Note the use of the replicator! to allow for multiple references to the same environment entry\*.

How does  $[[\lambda x M]]$  u receive its arguments? Along u it receives (as x) the name of its first argument, and also the name of a link where the rest will be transmitted. This explains the first line of Milner's encoding, which we now give in full:

$$[[\lambda x.M]] u \stackrel{\text{def}}{=} u(x)(v). [[M]] v$$

$$[[x]] u \stackrel{\text{def}}{=} \overline{x} u$$

$$[[MN]] u \stackrel{\text{def}}{=} (v) ([[M]] v | \overline{v}(x). \overline{v} u. [[x := N]])$$

Let us look, with Milner, at an example. We assume x is not free in N.

$$[[(\lambda x.x) N]] u \equiv (v) (v(x)(w). [[x]] w \mid \overline{v}(x). \overline{v} u. [[x:=N]])$$

(1)

<sup>\*</sup> In using the notation [[x := M]] for environment entries we follow [Mi92] but point out that it is distinct from the encoding function [[M]] u

$$\rightarrow \qquad (\nu)(x) \ (\nu(w). \ [[x]] \ w \mid \overline{\nu} \ u. \ [[x := N]]) \tag{2}$$

$$\rightarrow (x)([[x]] u \mid [[x := N]]) \tag{3}$$

$$\equiv (x) (\bar{x}u \mid !x(w). [[N]] w) \tag{4}$$

$$\rightarrow \qquad [[N]] \ u \mid (x) \ [[x := N]] \tag{5}$$

$$\sim [[N]] u \tag{6}$$

The following remarks help us read the above calculation:

- In (1), we have expanded the definitions for lambda abstraction and function application

- In (2), we have communicated a new channel x along v. Since x now occurs in both parallel subprocesses, the restriction (x) has been moved outwards to cover both occurrences.

- In (3), the restriction ( $\nu$ ) has been dropped because  $\nu$  no longer occurs

- The step to (4) represents the expansion of the definitions for identifier reference and environment entry

- In (5), (x) has been moved inwards as x now only occurs in the right subterm

- The last step, to (6), goes beyond simple equivalence and represents the garbage-collection of an environment entry [[x := N]] which cannot be used further (since the subject x of the first action is restricted).

Milner also provides a proof that the reduction of [[M]] in the  $\pi$ -calculus simulates that of M in the  $\lambda$ -calculus 'very closely'.

Reexamining the definition for environment entries [[x := M]] we observe that M is evaluated completely for each new set of arguments w. So while the scheme outlined above faithfully simulates normal-order reduction in the  $\lambda$ -calculus, it takes no account of sharing and thus does not model graph reduction as first defined by Wadsworth in [Wa71].

## 2.2.5 Simulating the call-by-value λ-calculus

Since the  $\pi$ -calculus is suitable for expressing concurrency, we would expect it to be able to express the parallelism implicit in the  $\lambda$ -calculus. Milner does so in his second encoding which simulates the call-by-value  $\lambda$ -calculus. Under call-by-value semantics we completely reduce an argument term before passing its value to a function. In the new encoding [[M]] p, the name p will have a different significance. The reason is that two 'events' which coincided for the normal-order calculus must now be separated, namely

- the signal at p that M has reduced to a value (needed when M is the argument of an application);

- the receipt of arguments by an abstraction M (needed when M is applied). Dealing with a call-by-value reduction strategy we will not need to pass 'apply nodes' as arguments, so our environment entries will now contain only values, i.e. abstractions and variables. So we begin by defining [[y := V]] where V is either a lambda abstraction or a variable.

$$[[y := \lambda x.M]] \stackrel{\text{def}}{=} !y(v). \ v(x)(p). \ [[M]] \ p$$

$$[[y := x]] \stackrel{\text{def}}{=} !y(v). \ \overline{x}v$$

An environment entry for an abstraction keeps reading new sets of arguments v to which the abstraction is to be applied. For each set thus received, we pick up the first argument, x, and the rest of the arguments, p. We instantiate a new copy of M to which we pass the arguments p. The first argument x is bound to the free variable x in M implicitly. An environment entry for a variable simple passes on any sets of arguments to that variable.

The first action of a (translated) value, [[V]] p, is to signal its reduction to a value. The channel y representing the signal provides access to an 'environment entry'. Note that [[y := V]] is here a *subterm* of [[V]] p, whereas the opposite was true in the normal-order encoding. In the most important

difference, however, to the normal-order encoding, the new translation  $[M \ N] p$  allows M and N to 'run' in parallel. The auxiliary definition ap(p, q, r) provides the necessary glue for relating functions to arguments: we pick up the value of M from q in the shape of an environment entry y and apply it to a new set of arguments v, which is constructed by extending the list of arguments p by the argument z computed by [N] r.

$$[[V]] p \stackrel{\text{def}}{=} \overline{p}(y). [[y := V]] \qquad (y \text{ not free in } V)$$

$$[[M N]] p \stackrel{\text{def}}{=} (q)(r) (\operatorname{ap}(p, q, r) + [[M]] q + [[N]] r)$$

$$\operatorname{ap}(p, q, r) \stackrel{\text{def}}{=} q(y). \overline{y}(v).r(z). \overline{v}zp$$

The example reduction sequence below for the  $\lambda$ -term  $(\lambda x.M)V$  demonstrates the simulation of  $\beta$ -reduction.

$$[[(\lambda z.M)V]] p \equiv (q)(r) (\operatorname{ap}(p, q, r) \mid \overline{q}(y). [[y:=\lambda z.M]] \mid \overline{r}(z). [[z:=V]])$$

$$\rightarrow (r)(y) (\overline{y}(v).r(z).\overline{v}zp \mid [[y:=\lambda z.M]] \mid \overline{r}(z). [[z:=V]]) \qquad (1)$$

$$\rightarrow (r)(y)(v) (r(z).\overline{v}zp \mid [[y:=\lambda z.M]] \mid v(z)(p).[[M]] p \mid (2)$$

$$\overline{r}(z).[[z:=V]]) \qquad (2)$$

$$\rightarrow (y)(z) ([[y:=\lambda z.M]] \mid [[M]] p \mid [[z:=V]])$$

$$\tag{4}$$

(3)

$(y)(v)(z) (\bar{v}zp \mid [[y:=\lambda z.M]] \mid v(z)(p).[[M]] p \mid [[z:=V]])$

$$\sim$$

(z) [[M]]  $p \mid [[z:=V]]$ ) (5)

Each of the four reduction steps consumes one of the actions defined by ap. The first step to (1) communicates the environment entry y for the functor  $\lambda z.M$ . Reduction (2) communicates the name v by which the functor can access its arguments. In step (3) we pick up the environment entry z for the argument V. Finally we make the extended argument set zp available via v.

The call-by-value nature of this scheme is apparent in the third and fourth actions of **ap**. The activation of a function call, performed by the action  $\overline{v}zp$ , cannot proceed until the argument to the function call signals its reduction to a value, detected by r(z). While this simulation exhibits

(some) parallelism in that for an application of the form MN both subterms can be evaluated in parallel, the application itself cannot proceed until the argument has been computed. Thus the parallelism implicit in a non-strict constructor function like cons which could return a result even before its argument values are available is not exploited by this scheme. More seriously, Milner's call-by-value scheme obviously has strict semantics and will thus fail to terminate for many terms which have a normal form.

We shall give a third encoding, combining the advantages of parallelism and non-strictness, in the next chapter.

## 2.3 The Manchester dataflow project

Making somewhat of a conceptual jump, we move from the theoretical domain of the  $\pi$ -calculus to computer architecture related research. The connection will be established in Chapters 3 to 6, where we develop a  $\pi$ -calculus specification of parallel graph reduction into a practical compiler for a novel parallel architecture.

Work on the Manchester dataflow machine is interesting to us mainly for their results on load bounding. In order to put these results into context, however, it will be useful to present a brief overview of the architectural side of the Manchester dataflow research. The architecture in itself is interesting as a major early example of a non-von Neumann machine that has been successfully implemented in hardware. While the similarities of the Manchester dataflow machine to our STAR:DUST architecture may not be immediately obvious, the latter can trace back its origins to the former in a direct line. This lineage will be illustrated in detail in Section 2.4.

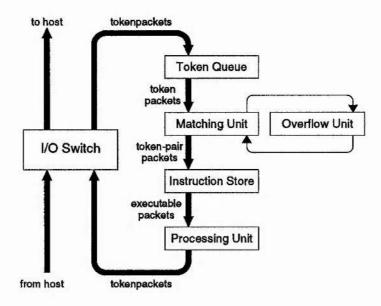

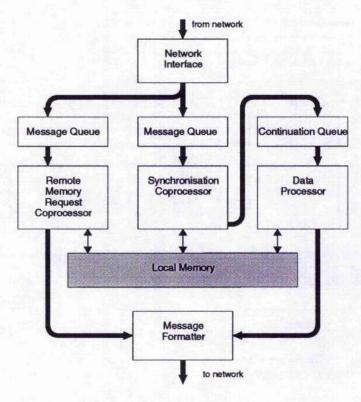

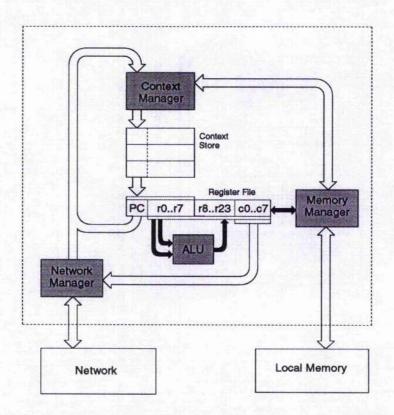

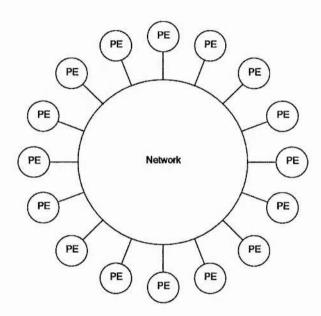

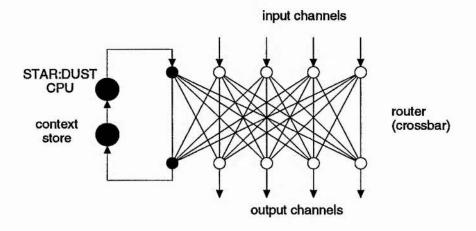

Figure 2.2: Structure of the Manchester dataflow system

#### 2.3.1 Architectural overview

We will present the Manchester dataflow architecture by relating it to modern von Neumann processor designs. In Figure 2.2 we show a single ring-structured dataflow processor connected via an I/O switch to a host computer as implemented by Gurd and his colleagues [GK85]. The system can be extended to a multiprocessor computer by widening the I/O switch to accommodate more processor rings. A good way to start thinking about an individual ring is as a processor pipeline, such as is commonly found in modern microprocessors. An important task in the design of such pipelines is to prevent instructions from being scheduled for execution when their operands have yet to be computed by instructions still in the pipeline. The Manchester pipeline provides an extremely clever conflict resolution mechanism which guarantees that an instruction cannot enter the pipeline before all its operand values are available. Other than in von Neumann microprocessors, however, instruction scheduling is governed solely by data dependencies of this kind. There is no concept of a program counter. Since the result produced by one instruction can satisfy the dependencies of more

than one successor instruction, multiple instructions can be ready for scheduling at the same time.

Let us follow the path of an imaginary token inserted by the host computer. The I/O switch which is responsible for directing the token to the appropriate dataflow processor (of which our system contains only one) sends it on to the token queue. This queue is a circular buffer that smoothes out uneven rates of generation and consumption of tokens in the ring. When reaching the head of the queue, the token is passed on to the matching unit, arguably the most unconventional component of the processor ring. The matching unit's prime responsibility is resolving instruction dependencies and scheduling instructions for execution. An incoming token carrying the first operand of a dyadic operation remains in the matching unit awaiting the arrival of its partner. The unit derives its name from this matching of partners. An incoming token that completes a match or is heading for a monadic operation is passed on to the instruction store which contains the program code. There the appropriate instruction is fetched and passed on along with the operands to the processing unit. Typically the processing unit is made up of several function units (akin to the multiple function units of a modern von Neumann processor), one of which will perform the required operation and generate one or two output tokens.

Note that the mechanism described above is readily expandable to multiple processing elements as the basic instruction scheduling mechanism is easily extended to work across processors. Note also that on our journey through the pipeline we did not encounter a stage which would obviously correspond to 'main memory access'. The matching unit implicitly provides the storage needed for data which would be kept in stack frames in a more conventional runtime model. For this reason the size of

the matching unit exceeds 1 M-words and is unsuitable for complete VLSI integration even with present-day technology. Furthermore the structure of the matching unit is relatively complex as it requires associative access to waiting tokens. In the Manchester machine this is implemented via a hardware hash-function. Some of the data storage functions were later moved from the matching unit to a dedicated *structure store*.

## 2.3.2 Load bounding in the Manchester dataflow machine

When the Manchester project was started, it had not yet become clear that many typical programs would provide sufficient parallelism to keep a large parallel machine busy. So it came originally as a surprise when it was observed that the amount of parallelism exhibited by some programs could get so large that the design of a throttle mechanism was crucially important in order to limit the resource requirements of such programs (see Section 1.7.2). The throttle designed by Ruggiero and Sargeant and described in [RS87] is a hardware device which operates roughly according to the following principles. On receiving a request for starting a new process their throttle decides, based on the level of parallel activity in the machine, whether to grant a new activation name or not. Parallel activity is measured in terms of the length of the token queue. If the machine is too busy, the process is suspended and is reactivated only when the level of activity has dropped. In order to promote depth-first execution, the first child of a process is never suspended. Given several suspended subprocesses for one process, the leftmost one is the first candidate for unsuspension. This order is guaranteed by a queueing strategy. They impose a small delay between individual unsuspensions since processes take a while to start up and have no immediate effect on the length of the token queues.

The Manchester throttle is responsible not just for load bounding but generally for resource management. Its functions include allocation of activation names, suspending and unsuspending of processes, activity level reports and termination signals. From a hardware point of view, the throttle is a message processor with an attached store and was implemented using the same design as for the structure store, with different microcode.

## 2.4 The MIT dataflow project

While work on the Manchester machine has now ceased, research into dataflow machines and languages is still actively being pursued at the Computation Structures Group at MIT. Originating with Jack Dennis's early work on a static dataflow machine [De75] which appeared radically different from any architecture known at the time, the MIT work has progressed in several stages, as outlined below, to a system designed around a commercial microprocessor. One of the results of their long and productive work was the P-RISC architecture which became a major influence for the design of STAR:DUST (Chapter 6). One purpose of this section is to illustrate that our STAR:DUST architecture, and thus the computational model underlying our compilation scheme, is not just a 'wild stab in the dark' but rather a combination of the core features of dataflow machines with the sequential efficiency of modern von Neumann architectures.

## 2.4.1 From static dataflow to Monsoon

Jack Dennis early work on static dataflow machines modelled the flow of streams of data through a static dataflow graph. The nodes of the graph represented operations which could 'fire' as soon as a complete set of inputs was available. While providing ample opportunity for parallelism, static dataflow graphs do not support a very general programming model. In particular, they do not allow for recursion. Dennis' 1973 paper [De73] is generally regarded as the seminal work inspiring dynamic dataflow which is capable of modelling graphs that are expanding and contracting

dynamically. Dynamic dataflow is thus suitable for modern recursive programming languages. The MIT work on dynamic dataflow machines was lead by Arvind, whose proposal for a dataflow architecture with tagged tokens [AK80] is substantially similar to the Manchester dataflow machine (but developed independently). Therefore we will not discuss it in detail here except for pointing out that it includes a waiting-matching unit requiring the same expensive fully associative matching capabilities for data sets. In contrast to the Manchester machine, the TTDA (tagged-token dataflow architecture) was never built in hardware.

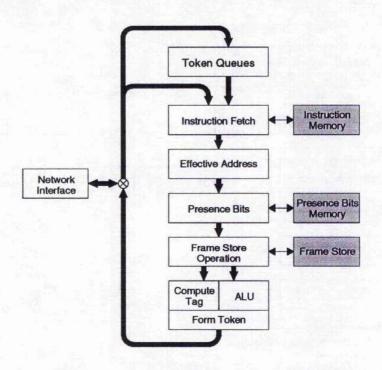

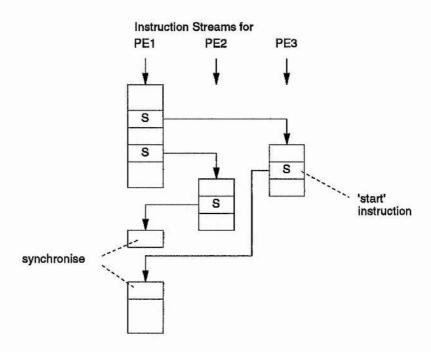

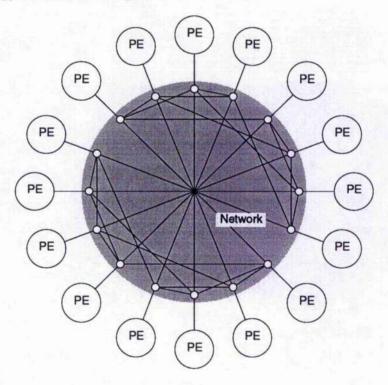

The first dataflow hardware at MIT became operational in 1988 in the form of the Monsoon machine [Pa88] which represents a substantial redesign of the original TTDA proposals. In Figure 2.3 we show the structure of a Monsoon processing element as presented in [PC90], redrawn to highlight the key differences from the Manchester architecture.

Figure 2.3: Structure of a Monsoon processing element

The fundamental improvement is the elimination of the waiting-matching unit which was achieved by making the token store *explicit*. Rather than relying on the storage of tokens to be performed implicitly and individually by hardware in the waiting-matching unit, storage allocation on Monsoon is performed by software and in units of procedure frames. An individual procedure frame is mapped wholly to a contiguous memory area within a *frame store*.

To understand the resulting changes in the operation of the processor pipeline consider the processing of a two-input operator (the following is largely quoted from [PC90]). The first token to be processed enters the pipeline and fetches the instruction specified in its tag field. During the effective address stage the location in the frame store where the match will take place is computed. The associated set of presence bits are examined and found to be in the 'empty' state. The presence state is thus set to 'full' and the incoming value is written into the frame store location during the frame store stage. Further processing of the token is suppressed because the other operand has yet to arrive. This 'bubbles' the pipeline for the remaining ALU stages; no tokens are produced during form-token, permitting a token to be removed from one of the token queues for processing. The second token to be processed enters the pipeline and fetches the same instruction. It therefore computes the same effective address. This time, however, the presence state is found to be 'full', so the frame store location (which now contains the value of the first token) is read and both values are processed by the ALU. Finally, one or two result tokens are created during the form-token stage.

Note that the pipeline of a Monsoon processing element is rather more similar to a conventional processor pipeline than that of the Manchester machine. An instruction fetch stage is followed by the computation of an effective address, a load/store stage interacting with local memory, and an ALU stage. There is even direct support for sequential execution by allowing successor instructions to bypass the token queue and re-enter the pipeline immediately. The differences to conventional pipelines are still significant, however: instructions can have multiple successors, all but one of which are stored in a token queue. The resulting parallelism is used to good effect to avoid bubbles in the pipeline. And finally, the stage responsible for 'presence bits' provides efficient hardware support for 'join' synchronisation.

## 2.4.2 Dataflow/von Neumann hybrid processors

The analogies between Monsoon and conventional processors were not lost on the MIT team. In [Ia88], Iannucci proposed the idea of dataflow machines and von Neumann machines sitting at opposite ends of a *spectrum* of architectures. The hybrid processor proposed in his paper travels another step towards von Neumann architectures by re-introducing registers as a very efficient means of communication for sequentially related instructions. (By constrast, Monsoon instructions can only send a single value to their successor in the form of a token. Where this is not sufficient, data have to be deposited in the frame store, i.e., in local memory.) By providing registers and dedicated instructions for testing and manipulating presence bits, Iannucci's hybrid processor can dispense with the idea of 'tagged tokens' for communication within a procedure frame.

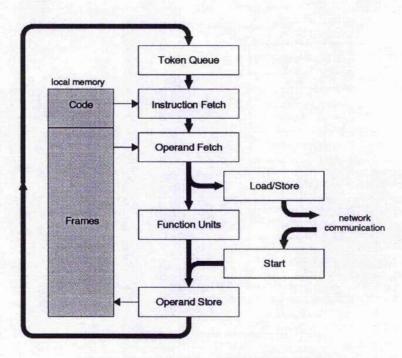

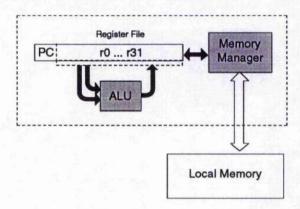

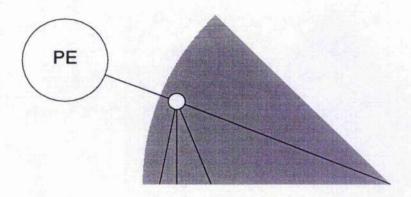

The next step in this process of evolution resulted from approaching the architectural spectrum from the opposite end by asking the question: how do we need to modify a von Neumann processor to make it suitable for efficiently executing dataflow programs? The design of the P-RISC architecture [AN88] which is shown in Figure 2.4 is an attempt to answer this question. P-RISC, short for 'parallel RISC', has at its core a plain

sequential RISC processor, i.e., three-address instructions, a load/store architecture, simple instruction formats, a program counter, conventional jump and branch instructions, etc. Addressing of operands is relative to a frame, which is best viewed as a fixed-size window providing fast access to local memory. The frame pointer along with the program counter make up the current continuation. Each of the conventional instructions has a single successor continuation which shares the frame pointer of its predecessor. All continuations operating within the same frame are considered to belong to the same thread.

Figure 2.4: A P-RISC processing element

The parallel extensions to the sequential RISC paradigm come in the shape of several simple new instructions which create, control and terminate threads.

fork produces an additional continuation which is placed in the token queue along with the natural successor

- join conditional termination of the current thread, i.e., depending on a condition, join has either one or zero continuations

- load reads a value from global memory; load has no immediate successor which allows other threads to keep the CPU busy during long-latency operations; the thread is restarted only on arrival of the value to be loaded

- store writes a value to global memory and continues with the next instruction; no synchronisation is performed

- loadc version of load with an implicit fork

- start sends a start message to a remote processing element; incoming start messages deposit a value into the local frame and place a continuation into the token queue (the arrival of values loaded from global memory is in the form of start messages)

A P-RISC system is made up of processing elements as discussed above as well as structure store elements which satisfy global read/write requests and perform low level synchronisation tasks and memory management functions. Comparing P-RISC with Monsoon we observe that the 'complex' dataflow instructions have been split into separate synchronisation, arithmetic and fork/control instructions, eliminating the necessity of presence bits in the frame memory.

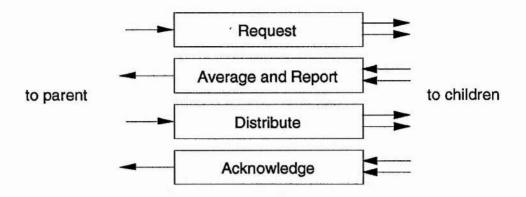

The (so far) final step in the MIT effort towards finding the optimal balance between dataflow and von Neumann processors is the \*T architecture [NP92], pronounced 'start', which is currently actively pursued in terms of hardware design (both Iannucci's hybrid architecture and P-RISC are 'paper architectures'). We show a block diagram of \*T in Figure 2.5.

Figure 2.5: The \*T architecture

The data processor in this diagram is a slightly enhanced version of the Motorola 88100, i.e., a commercial RISC microprocessor. The enhancements permit it to send messages to the network and to pick up new continuations (in the form of one word each for the program counter and a frame pointer). The data processor is responsible for the computational aspects of program execution. Two coprocessors sharing the same local memory are responsible for satisfying remote memory requests and synchronisation, respectively, without having to interfere with the data processor. Having a coprocessor for memory requests enables \*T to avoid the complications of providing dedicated structure store units. The synchronisation coprocessor (SP) handles returning loads by storing any returning value into its destination location. If the original load instruction is followed by a join synchronisation, the SP executes it and, if successful, places its continuation

on the continuation queue. Thus the data processor does not have to execute disruptive join instructions.

Being based on a standard microprocessor allows \*T to provide competitive performance for existing sequential code (which would execute wholly on the data processor) as well as for sequential portions of parallel code. It also permits \*T to 'ride the technology curve' by exploiting any advances in microprocessor design.

## 2.4.3 Load bounding for the MIT dataflow machines

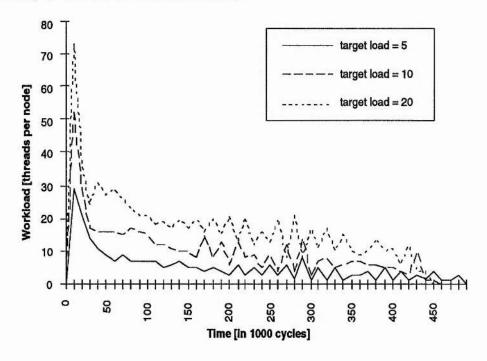

Supporting an implicitly parallel programming model, the MIT dataflow work needs to address the problem of excessive parallelism. In [CA88] Arvind and Culler propose the technique of *loop bounding* which controls parallelism resulting from those portions of loop iterations which are not constrained by dependencies on previous iterations. Their approach is, quite simply, to restrict for each loop the number of concurrently active iterations to some constant k, i.e., iteration n+k can begin only after iteration n has terminated. This solution appears to provide satisfactory results for many programs. Their compiler, as described in [TR86], generates parameterized code which allows the setting of loop bounds prior to execution, i.e., the choice of loop bounds is under user control and will typically depend on machine size, program type, and problem size.