# AN EMBEDDED CONTROL AND DISPLAY SYSTEM FOR A LASER-BASED MID-INFRARED HYPERSPECTRAL IMAGER

#### **Mark Ross**

# A Thesis Submitted for the Degree of MPhil at the University of St. Andrews

2009

# Full metadata for this item is available in the St Andrews Digital Research Repository

at:

https://research-repository.st-andrews.ac.uk/

Please use this identifier to cite or link to this item: http://hdl.handle.net/10023/731

This item is protected by original copyright

This item is licensed under a Creative Commons License

# An embedded control and display system for a laser-based mid-infrared hyperspectral imager

#### **Mark Ross**

A thesis submitted to the University of St Andrews in application for the degree of Master of Philosophy

18<sup>th</sup> July, 2008

Declarations

| I, Mark Ross, hereby certify th                                    | at this thesis, which is approximately 30,000 words in length, has been                                                                     |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| written by me, that it is the reco                                 | ord of work carried out by me and that it has not been submitted an any                                                                     |

| previous application for a higher                                  | degree.                                                                                                                                     |

| Date:                                                              | Signature of Candidate:                                                                                                                     |

| I was admitted for the part-time was carried out in the University | degree of M.Phil in April 2004; the higher study for which this is a record between 2004 and 2008.                                          |

| Date:                                                              | Signature of Candidate:                                                                                                                     |

|                                                                    | has fulfilled the conditions of the Resolution and Regulations appropriate fairness; and that the candidate is qualified to submit this ee. |

| Date:                                                              | Signature of Supervisor:                                                                                                                    |

Copyright Declarations

In submitting this thesis to the University of St Andrews I understand that I am giving permission for it to

be made available for use in accordance with regulations of the University Library for the time being in

force, subject to any copyright vested in the work not being affected thereby. I also understand that the title

and abstract will be published, and that a copy of the work may be made and supplied to a bona fide library

or research worker.

Date:

Signature of Candidate:

ii

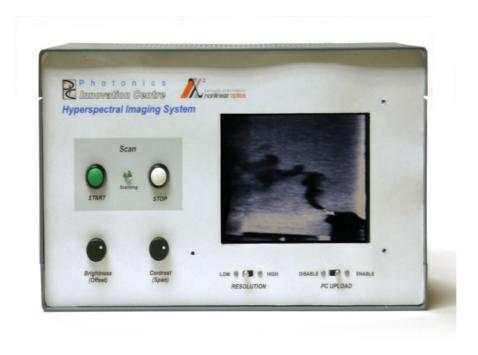

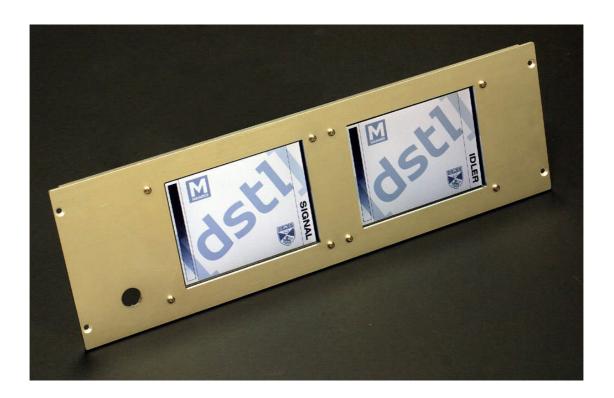

Back-scatter absorption gas imaging (BAGI) is a powerful laser-based detection technique whereby the strong spectroscopic absorption features in the gaseous species of interest are exploited in order to provide an image of the otherwise invisible (to the naked eye) gas. Such a device had been under development at the University of St. Andrews for the past three years. This thesis is concerned with the work carried out in the design, construction and testing of an electronic supervisory system for such a device to both control the electro-mechanical image acquisition hardware and display the image data upon an LCD module via an on-board video driver. Two different LCD display technologies, super twisted nematic (STN) and thin film transistor (TFT), have been demonstrated and their suitability for use in this system is assessed. It was found that the refresh rate and contrast ratio of the TFT display was greatly superior to that of the STN. Frame rates in excess of 10 fps have been demonstrated with this module. In addition to the scanner, a laser management system (LMS) was designed, constructed and tested to control the laser illumination system, which is based on an intracavity optical parametric oscillator (ICOPO). This involved the development of a dual-channel PID temperature controller to stabilise various optical components located within the ICOPO illumination source, a digitally-controlled constant current source to drive the pump diode laser and a digitally controlled system for an associated Q-switch driver module. The LMS was developed as part of the miniaturisation process and resulted in one dedicated instrument replacing six individual devices required in the laboratory demonstrator. The BAGI device has now been commercialised with elements of this research program being part of the overall instrument.

## Acknowledgements

I would like to thank Professor Malcolm H. Dunn for giving me the opportunity to undertake and supervise me in this Master of Philosophy degree as well as his extensive support and advice.

I would also like to extend special praise to Dr David J.M. Stothard whose all round guidance, encouragement, advice and patience was instrumental throughout the whole research program.

Many thanks also to my colleagues within the school of Physics and Astronomy, especially to both Mike Robertson for advice and encouragement throughout my working life and Jim Park who has given me invaluable training and played a major part in my career development. I would also like to thank Dr Cameron Rae who, during an informal chat, initially suggested that I may have the credentials to do a post graduate qualification of this nature. I would also like to show appreciation to Professor Steve Lee who has given me countless amounts of encouragement throughout his chairmanship of the school. His positive attitude to staff development and training allowed me to undertake this degree and indeed further my knowledge by agreeing for me to go on specialised training programs.

I would like to thank my mother Margaret and brother Mike whose support and tolerance, especially in the early part of the research program, was helpful and appreciated. I would also like to thank them for their all round support they have shown always shown towards me.

I would also like to thank my lovely wife Carolyn for all the love and support she has shown me as well as giving me encouragement, motivation and focus throughout the tougher moments of this research program.

Finally, I would also like to give special praise to my late father Alec, who sadly passed away just as this research program was undertaken, for the magnificent effort, support and encouragement shown to me throughout my life for which I will be eternally grateful.

I dedicate this thesis to my loved ones - my wife Carolyn, my mother Margaret, my brother Mike, my late father Alec and indeed our beautiful daughter Abbie who was born on 22nd August 2008.

# Table of contents

| Declarations |                                                        | i   |

|--------------|--------------------------------------------------------|-----|

|              | Abstract                                               | iii |

|              | Acknowledgements                                       | iv  |

|              | Table of contents                                      | vi  |

| Cho          | apter One - Introduction                               |     |

| 1.1          | Back-Scatter Absorption Gas Imager (BAGI)              | 1   |

| 1.2          | Advantages of a BAGI system                            | 1   |

| 1.3          | Methane Detection with a BAGI system                   | 2   |

| 1.4          | BAGI Components                                        | 3   |

|              | 1.4.1 Optical Parametric Oscillators                   | 3   |

|              | 1.4.2 The Imaging System                               | 6   |

|              | 1.4.2.1 Polygonal Scanner                              | 8   |

| 1.5          | Research Programme Outline                             | 11  |

|              | References                                             | 12  |

| Cha          | apter Two – Data Acquisition and LCD Controller (DALC) |     |

|              |                                                        |     |

| Sys          | tem                                                    |     |

|              |                                                        |     |

| 2.1          | Introduction                                           | 14  |

| 2.2          | Data Acquisition LCD Controller System                 | 15  |

|              | 2.2.1 Internal Data Acquisition                        | 16  |

|              | 2.2.2 External Data Acquisition.                       | 16  |

| 2.3          | Micro-controller Unit.                                 | 19  |

|              | 2.3.1 Micro-Controller Unit Configuration              | 19  |

| 2.4          | Graphic Controller                                     | 21  |

|              | 2.4.1 S1D13706 Bus Configuration                       | 22  |

|              | 2.4.2 S1D13706 Clock Configuration                                                                                                                                                                                                                                                                                                      | 23                                                 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|              | 2.4.3 S1D13706 Configuration Options                                                                                                                                                                                                                                                                                                    | 24                                                 |

|              | 2.4.4 Refresh rate calculation.                                                                                                                                                                                                                                                                                                         | 26                                                 |

| <b>2.5</b> A | Analogue to Digital Converter Channels                                                                                                                                                                                                                                                                                                  | 28                                                 |

|              | 2.5.1 Separating Analogue and Digital Grounds for Noise Reduction                                                                                                                                                                                                                                                                       | 30                                                 |

| 2.6          | Digital to Analogue Converter                                                                                                                                                                                                                                                                                                           | 32                                                 |

| 2.7          | EPROM                                                                                                                                                                                                                                                                                                                                   | 32                                                 |

| 2.8          | RAM                                                                                                                                                                                                                                                                                                                                     | 35                                                 |

| 2.9          | LCD panel, CCFL and Inverter                                                                                                                                                                                                                                                                                                            | 36                                                 |

|              | 2.9.1 Basic Passive Matrix Operation.                                                                                                                                                                                                                                                                                                   | 36                                                 |

|              | 2.9.2 Basic active matrix displays                                                                                                                                                                                                                                                                                                      | 37                                                 |

|              | 2.9.3 CCFL and Inverter                                                                                                                                                                                                                                                                                                                 | 38                                                 |

| 2.10         | External Data Acquisition Interface                                                                                                                                                                                                                                                                                                     | 41                                                 |

| 2.11         | Software Control                                                                                                                                                                                                                                                                                                                        | 42                                                 |

| 2.12         | Results                                                                                                                                                                                                                                                                                                                                 | 46                                                 |

| 2.13         | Summary                                                                                                                                                                                                                                                                                                                                 | 48                                                 |

|              |                                                                                                                                                                                                                                                                                                                                         |                                                    |

|              | References                                                                                                                                                                                                                                                                                                                              | 48                                                 |

|              | References                                                                                                                                                                                                                                                                                                                              | 48                                                 |

|              | apter Three: Image Acquisition Display (IADD) System &                                                                                                                                                                                                                                                                                  |                                                    |

| Ran          | apter Three: Image Acquisition Display (IADD) System & adom Access LCD System (RAL)                                                                                                                                                                                                                                                     | 50                                                 |

| 3.1          | apter Three: Image Acquisition Display (IADD) System & adom Access LCD System (RAL)  Introduction                                                                                                                                                                                                                                       | 50<br>51                                           |

| 3.1          | apter Three: Image Acquisition Display (IADD) System & adom Access LCD System (RAL)  Introduction                                                                                                                                                                                                                                       | 50<br>51<br>52                                     |

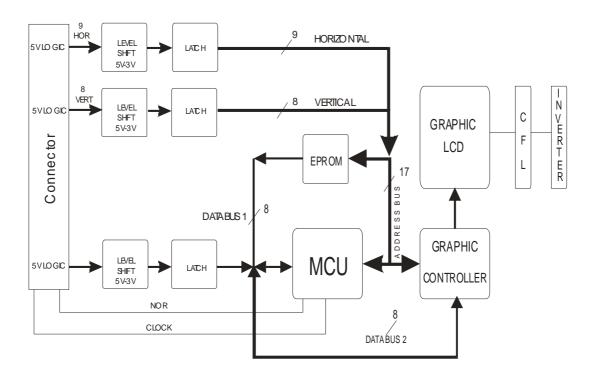

| 3.1<br>3.2   | Introduction.  Data acquisition display processing system (IADD).  3.2.1 Components of the IADD system.                                                                                                                                                                                                                                 | 50<br>51<br>52<br>54                               |

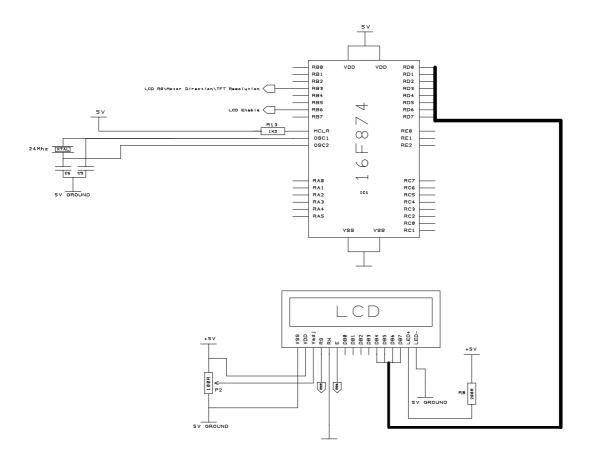

| 3.1<br>3.2   | Introduction.  Data acquisition display processing system (IADD).  3.2.1 Components of the IADD system.  Micro-Controller Unit.                                                                                                                                                                                                         | 50<br>51<br>52<br>54<br>54                         |

| 3.1<br>3.2   | Introduction.  Data acquisition display processing system (IADD).  3.2.1 Components of the IADD system.  Micro-Controller Unit.  3.3.1 Micro-Controller Configuration.                                                                                                                                                                  | 50<br>51<br>52<br>54<br>54<br>56                   |

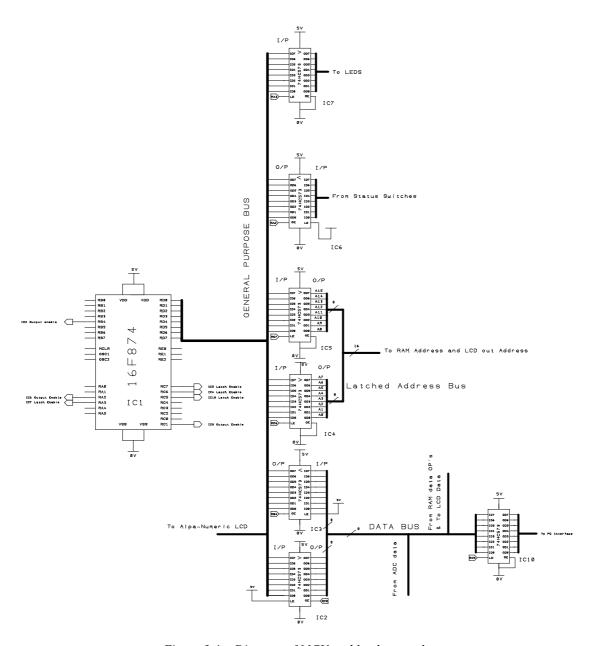

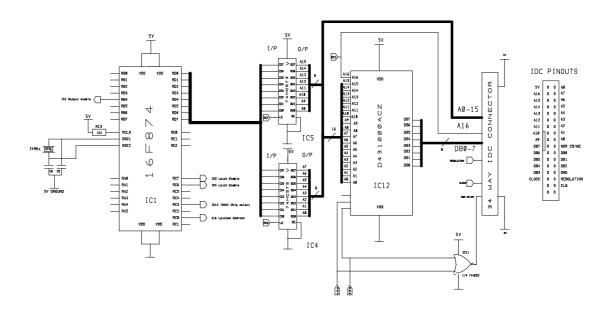

| 3.1<br>3.2   | Introduction.  Data acquisition display processing system (IADD).  3.2.1 Components of the IADD system.  Micro-Controller Unit  3.3.1 Micro-Controller Configuration  3.3.2 Micro-Controller and bus control                                                                                                                            | 500<br>511<br>522<br>544<br>546<br>577             |

| 3.1<br>3.2   | Introduction.  Data acquisition display processing system (IADD).  3.2.1 Components of the IADD system.  Micro-Controller Unit.  3.3.1 Micro-Controller Configuration.  3.3.2 Micro-Controller and bus control.  3.3.3 Micro-Controller and random access memory control.                                                               | 50<br>51<br>52<br>54<br>54<br>56<br>57<br>58       |

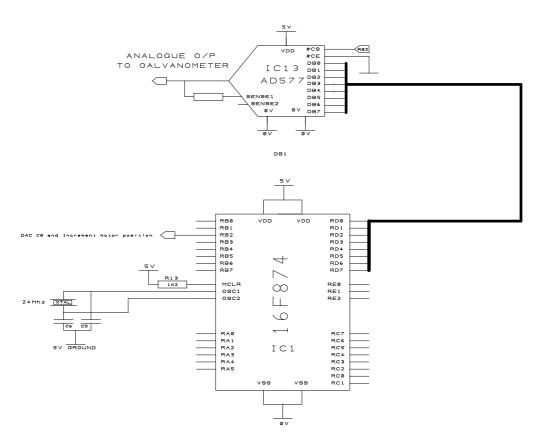

| 3.1<br>3.2   | Introduction.  Data acquisition display processing system (IADD).  3.2.1 Components of the IADD system.  Micro-Controller Unit  3.3.1 Micro-Controller Configuration  3.3.2 Micro-Controller and bus control  3.3.3 Micro-Controller and random access memory control  3.3.4 Micro-Controller and digital to analogue converter control | 50<br>51<br>52<br>54<br>54<br>56<br>57<br>58<br>59 |

| 3.4 | Random access LCD system (RAL)        | 63        |

|-----|---------------------------------------|-----------|

|     | 3.4.1 Components of the RAL system    | 64        |

| 3.5 | RAL system operation                  | 65        |

|     | 3.5.1 RAL and DALC system differences | 67        |

| 3.6 | Chapter 3 results                     | 72        |

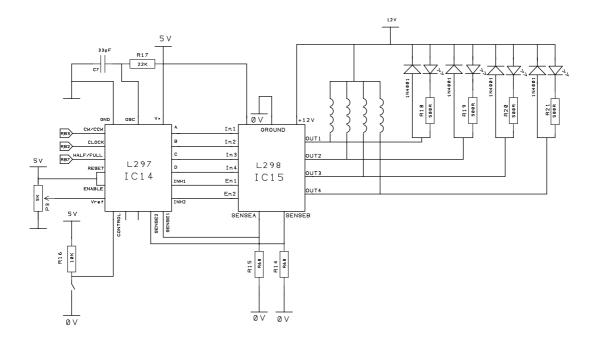

|     | 3.6.1 Stepper motor                   | 72        |

|     | 3.6.2 Performance of the IADD system  | 74        |

|     | 3.6.3 Performance of the RAL system   | 74        |

| 3.7 | Summary                               | 77        |

|     | References                            | <b>78</b> |

# Chapter Four – Laser Management System (LMS)

| 4.1 | Introduction                                                        | 80  |

|-----|---------------------------------------------------------------------|-----|

| 4.2 | The parametric process, quasi phase-matching and temperature tuning | 80  |

| 4.3 | Laser Management System                                             | 85  |

| 4.4 | Brief description of LMS components                                 | 87  |

| 4.5 | Electronic System Design                                            | 88  |

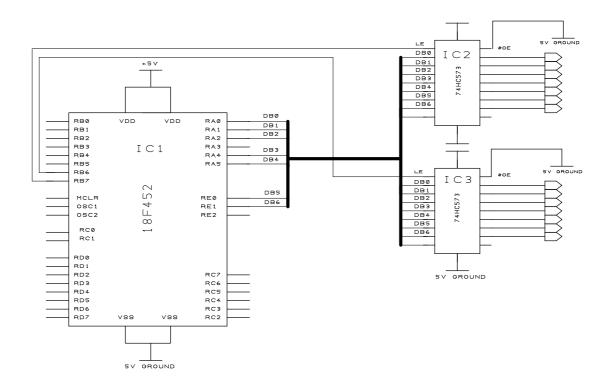

|     | 4.5.1. Basic MCU hardware setup                                     | 89  |

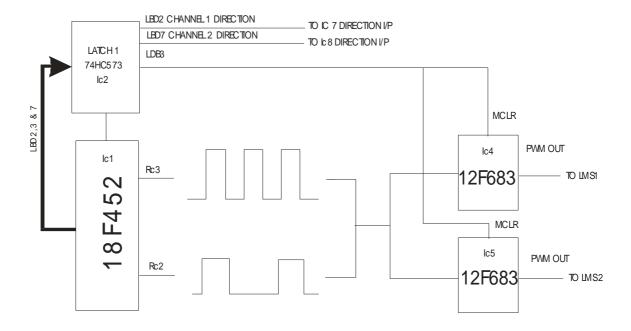

|     | 4.5.2 MCU and latch connections                                     | 90  |

|     | 4.5.3 PWM Generation                                                | 92  |

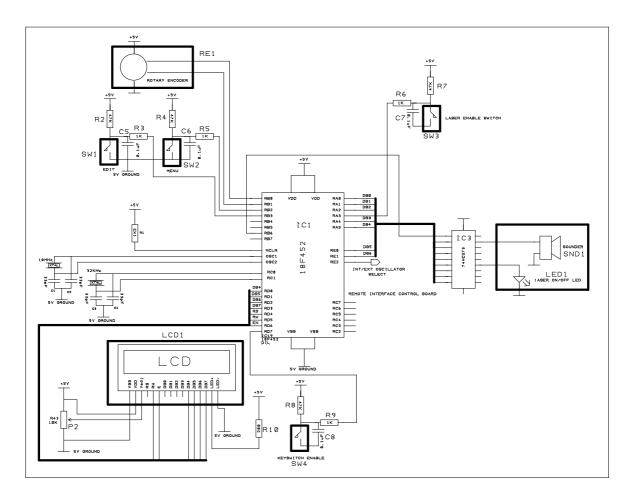

|     | 4.5.4 Front Panel Hardware Interface                                | 94  |

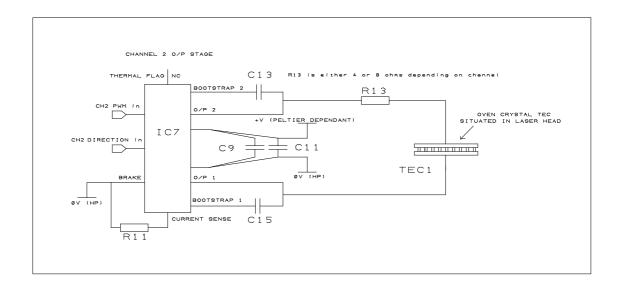

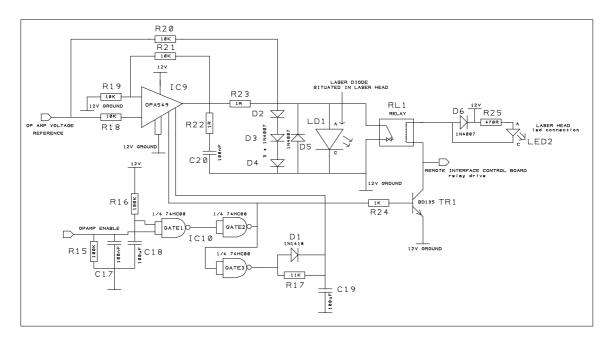

|     | 4.5.5 Dual channel TEC Drive                                        | 95  |

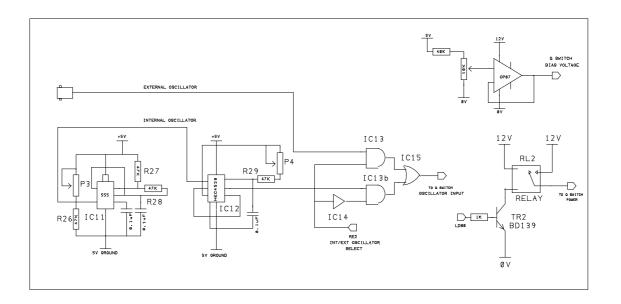

|     | 4.5.6 Q Switch Driver Associated Electronics                        | 96  |

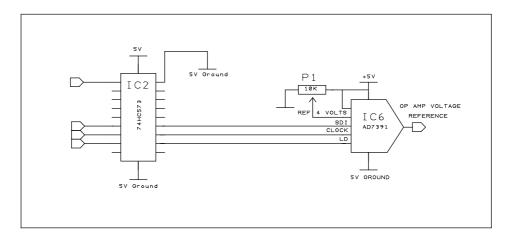

|     | 4.5.7 Laser Diode Drive and DAC                                     | 97  |

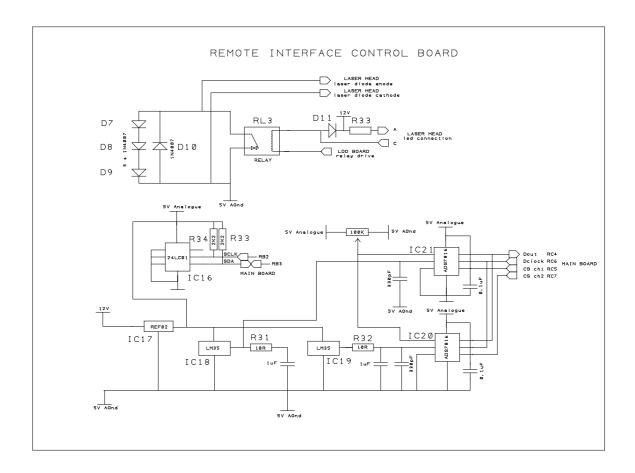

|     | 4.5.8 Remote Interface Control Board                                | 99  |

| 4.6 | Software Used In the LMS System                                     | 101 |

|     | 4.6.1 Interaction of Software                                       | 101 |

|     | 4.6.2 The C Compiler                                                | 102 |

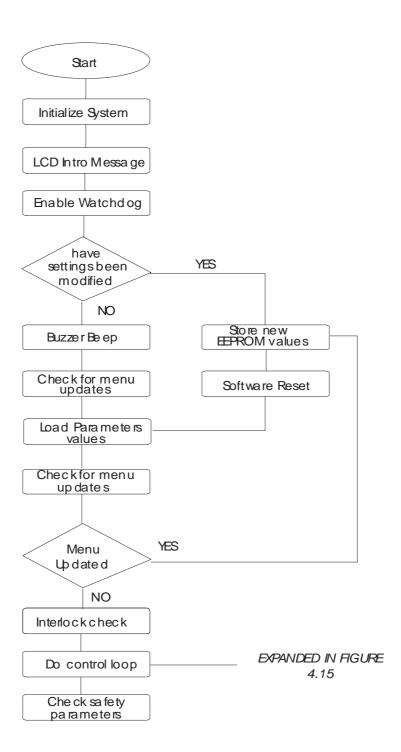

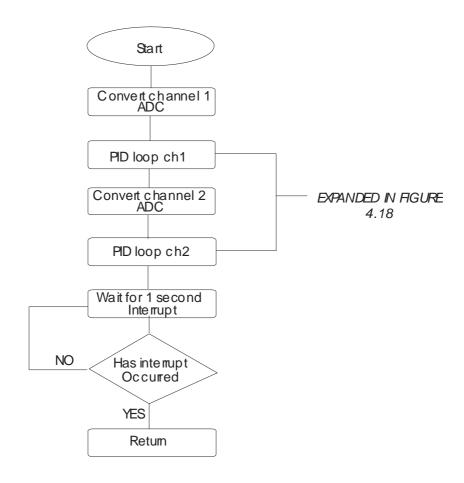

|     | 4.6.3 Flowcharts of code execution                                  | 104 |

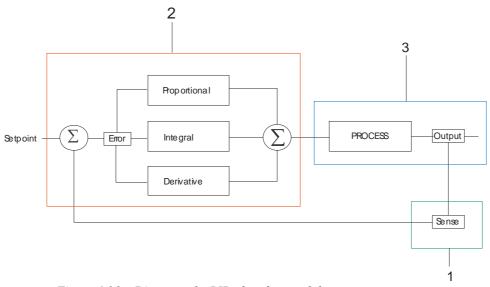

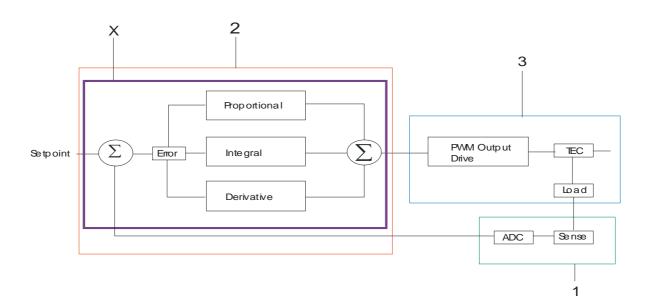

| 4.7 | PID Controller                                                      | 105 |

|     | 4.7.1 TEC Control Loop.                                             | 107 |

|     | 4.7.2 Digital PID Loop.                                             | 108 |

| 4.8 | Tuning Methods of a PID System & System Performance Results         | 110 |

| 4.9 | Summary                                                             |     |

|     | References                                                          |     |

|     |                                                                     |     |

## Chapter Five – Conclusions

| 5.1        | Introduction                                                    | 124 |

|------------|-----------------------------------------------------------------|-----|

| 5.2        | Background of work                                              | 124 |

| 5.3        | Synopsis of work carried out                                    | 125 |

| 5.4        | Further work                                                    | 128 |

| 5.5        | Summary                                                         | 130 |

|            | References                                                      | 131 |

| Арр        | pendix A                                                        |     |

| Proj       | ject schematic diagrams and printed circuit board (PCB) layouts | 132 |

| <i>App</i> | pendix B                                                        |     |

| Proj       | ject firmware code                                              | 132 |

| Арр        | pendix C                                                        |     |

| Con        | ference proceedings                                             | 133 |

| Арр        | pendix D                                                        |     |

|            |                                                                 |     |

Digital appendices CD Rom

#### 1.1 Back-Scatter Absorption Gas Imager (BAGI)

Research at the University of St Andrews has led to the development of a Backscatter Absorption Gas Imaging (BAGI) system [1,2,9] based on a novel laser source, and this system is currently being constructed for field testing as a man portable instrument. Crucial to this is the development of a dedicated electronic system capable of controlling the electro-mechanical hardware. This hardware was previously developed in readiness for demonstration and commercialisation in the near future, within the context of a portable standalone instrument. The present project is concerned with meeting these objectives through the design and realisation of electronic hardware and embedded software upon which it will depend. The micro-controlled data acquisition & visual display system and the supervisory laser management hardware are described in this report.

#### 1.2 Advantages of a BAGI system

Gas detection is very important for many reasons from environmental and economic issues to life threatening situations and so the quicker an unwanted leak can be isolated and serviced, the chances of a serious incident involving such a leak are minimised. Current gas detection techniques are based around technologies such as gas chromatography or electronic 'point and sniff' detectors. Such techniques have adequate sensitivity and (in the case of electronic gas detectors) portability and so are ideal in a number of small-scale, low cost (for instance, domestic) applications. However, as they simply measure point concentration of the gaseous species under investigation, very little feedback is given to the operator as to the source of the leak. This can prove extremely problematic when gas leaks are detected in very large scale industrial installations. A visual picture, relayed to the operator in real time, which indicated both the presence *and position* of the detected gas would be highly desirable, and it is this feature which is exploited in the BAGI technique. Gas imaging obtains instant results helping to source the location of the leak as well as an indication of its severity.

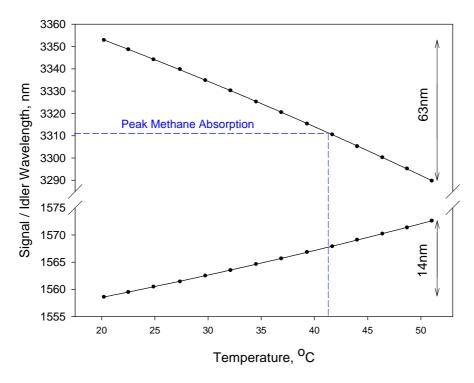

#### 1.3 Methane Detection with a BAGI system

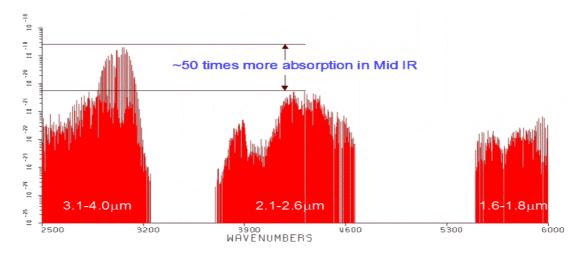

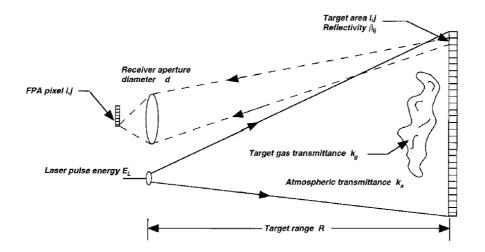

The gas investigated for detection in this research project is methane (CH<sub>4</sub>) because it is a widely used source of cheap energy found in both domestic and industrial environments. The main disadvantages of methane are that it is highly explosive when mixed with air, is a potent greenhouse gas and thus damaging to the environment and is a colourless, odourless (in its native form) molecule which is completely invisible to the human eye. The BAGI method of detection depends upon the gaseous species of interest exhibiting strong optical absorption at some illumination wavelength. In the case of methane, the highest absorption coefficients are located in the mid-infrared region at ~3.31µm, as shown in figure 1.1. The idea underpinning the BAGI technique is that if a powerful light source, of sufficient spectral purity and with a wavelength coincident with these absorption features is used to illuminate an area, any methane present within its illuminated area would very strongly absorb this light. Light not absorbed by the gas (i.e. where no gas is present) would be back-scattered (for example, from walls or pipes) and this could be collected and imaged, thus allowing the visualisation of methane. This technique is shown in figure 1.2.

#### Label y axis $log\alpha(A.U)$

Figure 1.1: Methane absorption wavelengths [3]

#### 1.4 BAGI Components

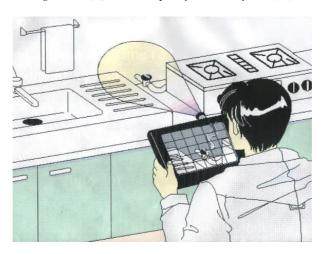

Gas detection with the BAGI technique requires two key sub systems; a powerful mid-infrared laser source (ideally tunable) for scene illumination and an imaging system with which to visualise the back-scattered light.

Current conventional laser systems operating in the mid-infrared band are typically characterised by low power output, very poor tunability, excessive system complexity and cost, or a combination of these. For instance, whilst lead-salt (PbS) laser diodes are relatively low cost and offer moderate temperature tunability, they emit very low (<1 mW) power and need to be cryogenically cooled in order to operate. The mid-infrared Helium-Neon laser offers more power (up to ~10 mW) but is inefficient, bulky, fragile and cannot be tuned into different absorption transitions. Clearly, a laser system exhibiting tunable, narrow linewidth and high output power characteristics from a compact, all solid-state geometry would be highly desirable in the context of this application.

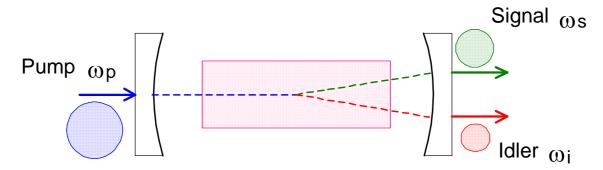

#### 1.4.1 Optical Parametric Oscillators

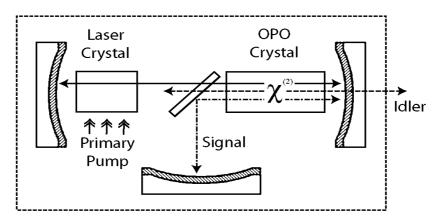

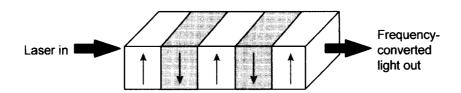

The technique used to achieve the power and wavelength agility required for this application in the mid-infrared spectral band is a pulsed Optical Parametric Oscillator (OPO). This development of this optical source was largely carried out before the onset of this research project and a detailed description of the physics processes underpinning its operation is somewhat outside the scope of this report. However, the basic principles of operation are briefly outlined here. The parametric process is a non-linear optical effect which operates by taking a high energy (short wavelength) photon and "splitting" it into two lower energy, and therefore longer wavelength, photons as depicted in figure 1.3. These generated photons are called the signal and idler photons, with the idler the longer wavelength of the two. By changing the properties of the non-linear crystal (for instance, it's temperature) the wavelengths of the signal and idler can be changed, and hence any system utilising an OPO is tunable even if the laser upon which it is based is not. In this system, the wavelength of the idler wave is tuned into the methane absorption features of interest.

Figure 1.2 (a): An example of a BAGI system [1]

Figure 1.2 (b): Implementation of the BAGI technique

Figure 1.3: The parametric process.

Traditionally, these devices have required somewhat excessively high input powers to reach threshold or have suffered serious stability issues. The solution to this is to place the OPO within the optical cavity of the pump laser and hence take advantage of the very high pump field found there, shown in figure 1.4.

Whilst the *intracavity OPO* (ICOPO) can be made to operate in a continuous-wave mode [4,5] the system utilised in this project was pulsed by the inclusion of an acousto-optic Q-switching element within the pump cavity to stabilise the transient dynamics of the laser. The system is capable of producing ~150 mW of broadly-tunable peak idler power at a repetition rate of >350 kHz. As we shall see later on in this report, careful triggering of the Q-switching element is required in order to synchronise the production of optical pulses with spatial pixel points.

Figure 1.4: OPO inside a laser cavity, the Intracavity OPO (ICOPO).

Tuning of the idler wavelength is achieved through varying the temperature (and therefore, the refractive index) of the non-linear crystal. Hence, in order to get stable and variable wavelength output, careful temperature control of the nonlinear crystal via thermo-electric cooling is necessary.

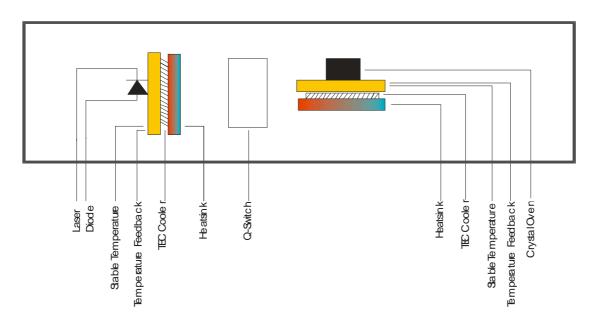

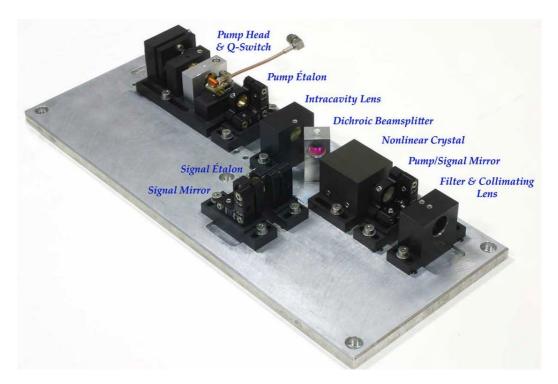

The OPO system [6,7] is optically pumped by a 3 W continuous wave (CW) laser diode operating at 808.5 nm. It is important that the wavelength output of the diode closely matches that of the absorption manifold of the laser gain medium. Therefore, it is again important to provide temperature stabilisation of this component, as the bandgap and hence output wavelength of the semiconductor diode is a function of its operating temperature. The operation of laser diodes is closely analogous to that of light emitting diodes (LED). As with the LED, a constant current supply is necessary for reliable operation. In this particular case a current supply of up to 3.5 A with a compliance voltage of 2.5 V is required. Therefore a supervisory system is required achieve this dual-channel temperature control (for the laser diode and nonlinear optical crystal) and constant current supply. A schematic diagram of the OPO components that require driving by external electronic systems is shown in figure 1.5 and an annotated photograph of the laser system is shown in figure 1.6.

Figure 1.5: Block diagram of OPO components which require electronic interaction.

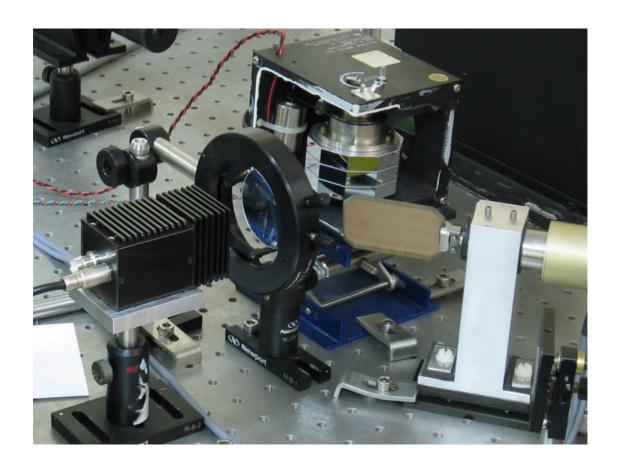

Figure 1.6: Photograph of the ICOPO system. The illuminating mid-infrared beam exits the system through the pump/signal mirror.

#### 1. 4. 2 The Imaging System

With the illumination source for the BAGI detector sufficiently developed our attention now turns to the imaging system. A conventional imaging device utilises a two-dimensional video array of photodetectors to make a camera and for this application it might appear that a suitably sensitive midinfrared camera would be ideal. Unfortunately, cameras operating over this band, with sufficient sensitivity, are based upon mercury-cadmium-telluride (MCT) or Indium antimonide (InSb) arrays which require cryogenic cooling. Methods of cooling are either liquid nitrogen or miniature stirling engine heat pumps. These cameras are prohibitively expensive: approximately £50,000 per unit [8]. Such cost and complexity precludes the use of these cameras in this project. As such, an alternative image acquisition system is required.

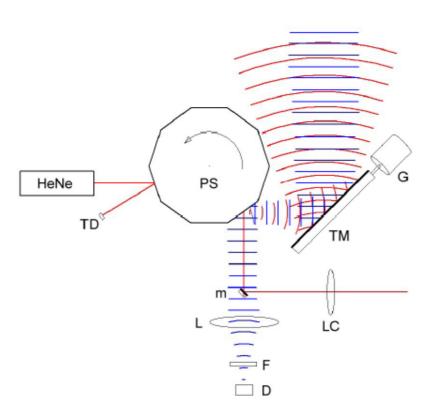

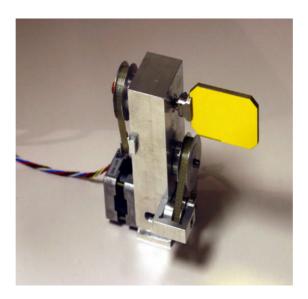

This alternative is an electro-mechanical scanner based upon a rotating polygonal mirror and reciprocating galvanometer mirror. The idler beam is rapidly raster-scanned over the scene of interest and the amount of back-scattered light is collected and measured at each pixel point in order to build up the image. Such a system has the advantage of low cost (only a single element photodetector is required) and very good signal-to-noise ratio as each pixel point is measured with the full idler power incident upon it.

Figure 1.7: Polygon scanner schematic [9]

#### 1.4.2.1 Polygonal Scanner

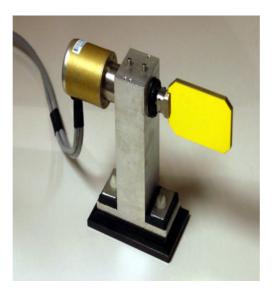

The geometry of the scanner used for imaging is shown in figure 1.7. Illuminating radiation from the optical parametric oscillator is directed along the optical axis of the arrangement by a small plane mirror m placed on-axis in front of the calcium fluoride collection lens L and then by the polygonal scanner PS which has 10 facets and tilting mirror TM to the scene under surveillance. The backscattered radiation returning from the scene is collected via the same tilting mirror and polygon scanner and is then focused by the collection lens onto the MCT detector D located in the image plane of the collection lens. The area of the collection lens is sufficient such that the effective limiting collection aperture for the returned signal occurs at the polygon mirror facet. It is desirable to keep the area of the galvanometer mirror, polygon mirror facet and lens as large as possible in order to maximise the collected light and hence the subsequent measured signal. The above arrangement ensures that the detector always views that area of the scene currently being illuminated by the scanned idler beam from the optical parametric oscillator (i.e., the viewing direction is scanned in spatial synchronism with the illuminating beam). The calcium fluoride lens LC placed before the mirror m collimates the diverging idler beam. Since the MCT detector employed exhibits sensitivity over a broad range of wavelengths, a band pass filter F is placed in close proximity to the detector active area in order to reject stray infrared radiation from hot objects, laboratory lights and pump and signal fields that are leaked through OPO output mirror. A Helium-Neon or low-cost visible diode laser and detector **TD** are employed in order to trigger the image acquisition electronics at the correct point of the polygon rotation when scanning a horizontal line. A photograph of the polygon scanner mounted upon an optical bench is shown in figure 1.8.

A sample image acquired using this polygonal scanning system / OPO source, with the idler tuned into the peak absorption cluster in methane at  $3.31\mu m$ , is shown in figure 1.9. In it the leaking gas is clearly visible. In it, the skin of the operator appears dark due to the high water content (and therefore absorption coefficient). It is also noticeable how dark the operators' spectacles are, demonstrating the need for optical components specially chosen for their high transmission properties in the min-infrared, for instance the calcium fluoride lenses.

Figure 1.8: Photograph of the Polygon Scanner.

Figure 1.9: Sample image, acquired in the visible (left) and at 3.31 µm using the polygonal scanner [9]

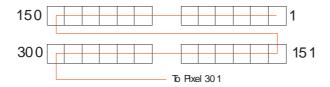

The imaging system scans the area under surveillance by means of an X-Y grid. The X component of the grid is controlled by the polygon and the Y component by the galvanometer. The grid comprises 150 horizontal samples by 100 vertical samples. The galvanometer scans both directions of the Y plane in order to save time by obviating the need to 'fly-back' the mirror. Figure 1.10 (a) highlights the order of sampling in the down direction with Figure 1.10 (b) showing the order of sampling in the up direction. It can be seen from this how vital time is saved by scanning in both directions. After the down scan is complete the galvanometer is already in position to start the up scan and vice versa

Figure 1.10(a): Order of sample acquisition in down scan

Figure 1.10(b): Order of sample acquisition in the up scan. Note the same direction of the x-scan due to the singular directional action of the polygon and the opposing direction of the y-scan due to the bidirectional action of the galvanometer.

At each pixel point, an optical pulse is emitted from the OPO, directed out into the scene of interest via the polygon and galvanometer, and its back-scattered signal is re-collected and focussed onto the detector where it produces an analogue signal. Areas with bright reflective type surfaces produce high signal levels and dark areas which exhibit high absorption produce lower levels of signal. methane has a very high absorptive properties with the OPO tuned to 3.31µm thus returning very low signal levels or indeed zero depending on the concentration of the gas. The analogue signal levels are converted to 8 bit digital values with 0 indicating the lowest detected signal and 255 indicating the highest. An analogue to digital (A/D) converter processes the signal into digital format. The sample data is stored into electronic memory and this data is continually downloaded onto a PC with specialist software to display the data in the X-Y image format shown in Figures 1.10 (a) and 1.10 (b).

#### 1.5 Research Programme Outline

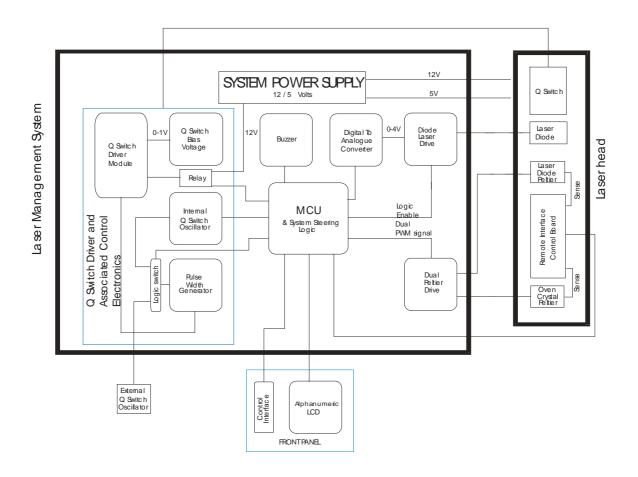

Such a scheme, whereby the image is acquired and stored in a bespoke electronic subsystem before uploading to a PC for display was acceptable in the infancy of this project, when the optical properties of the OPO were being investigated and optimised, but now this has been largely achieved it is highly desirable to remove the need for the host PC. This would be achieved by realising in-house designs for image acquisition, display driving and a high-resolution in-built LCD module for display. Such hardware will enable the eventual portability of the instrument for in-field testing. Also, during this initial research stage for the development of the OPO, discrete instrumentation was employed to drive the various components within the laser system. These included a Q-switch driver and associated signal generator, two separate temperature controllers for the nonlinear crystal and pump diode, a constant current source and various pieces of diagnostic equipment. Clearly, the portability of the scanner is severely compromised by the reliance of its illumination source on so many pieces of instrumentation. The second phase of this research programme, therefore, involved the realisation of a single driver device which could perform all of the functions previously described.

It is precisely the design and realisation of this electronic hardware, and the embedded microprocessor software upon which it depends is detailed in the following chapters.

Chapter 2 describes the early investigation undertaken to drive high resolution LCD displays. The two main display technologies available today, super twisted nematic (STN) and thin film transistor (TFT), are compared and contrasted for suitability for use within this project. Video driver integrated circuits are evaluated in the context of embedded processor control. Finally, the display technology of choice was integrated into a first prototype image acquisition system which had the capability to be interfaced to the scanning electronics developed prior to this project, or to be used as a stand-alone system.

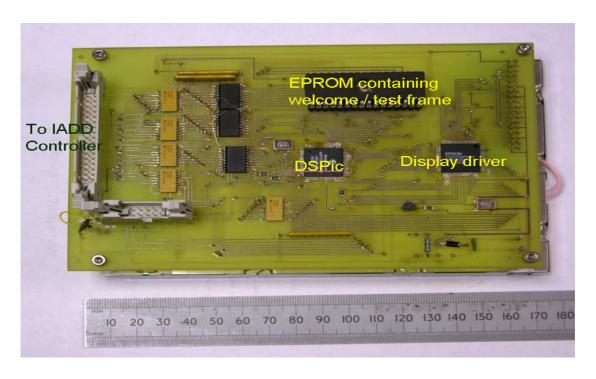

The work undertaken in chapter 2 indicates the logical progression of the display and driver into a stand-alone module which had a RAM chip like electronic interface and could therefore easily be interfaced to a variety of microprocessor-based designs. In this way, the display driver technology could be perfected and easily produced and used in many different applications, not just restricted to

this one. The modular approach therefore split the design of the image display electronics into two main subsystems: the image acquisition (for control of the scanner electro-mechanical hardware) and the image display boards. The development integration and operation of these are described in chapter 3.

The design and realisation of the laser management system, which comprises a dual channel closed-loop temperature controller, constant current source and high repetition rate RF Q-switching system, is described in chapter 4. Here, the PID temperature control algorithm is described and a simple mathematical treatment is presented. The tuning of the PID loop for this particular device is also described.

The result of this research programme with be briefly summerised in chapter 5 and indications given into possible further avenues of work which would lead to performance improvements.

#### **Chapter 1 References**

- [1] Kulp, T.J., et al., Development of a pulsed backscatter-absorption gas-imaging system and its application to the visualization of natural gas leaks. Applied Optics, 1998. 37(18): p. 3912-3922.

- [2] McRae, T.G. and T.J. Kulp, *Backscatter Absorption Gas Imaging a New Technique for Gas Visualization*. Applied Optics, 1993. **32**(21): p. 4037-4050.

- [3] HITRAN spectroscopic database, ONTAR corporation 1996.

- [4] Stothard, D.J.M., M. Ebrahimzadeh, and M.H. Dunn, *Low pump threshold, continuous-wave, singly resonant, optical parametric oscillator.* Opt. Lett., 1998. **23**: p. 1895.

- [5] Colville, F.G., M.H. Dunn, and M. Ebrahimzadeh, *Continuous-wave, singly resonant, intracavity parametric oscillator*. Opt. Lett., 1997. **22**(2): p. 75.

- [6] Stothard, D.J.M., C.F. Rae and M.H.Dunn, "An intracavity optical parametric oscillator with very high repetition rate and broad tenability upon room temperature periodically-poled MgO:LiNbO<sub>3</sub> with fanned grating design," submitted to IEEE. J.Quant. Elect., May 2008.

- [7] D. J. M. Stothard, C. F. Rae, M. Ross and M. H. Dunn, "Compact, all solid-state, high repetition rate intracavity optical parametric oscillator and its application to the spectroscopic imaging of gases and liquids," paper CTuU3, Conference on lasers and electro-optics 2007, Baltimore, USA, May 2007.

- [8] George Bailey, THALES electro-optics corporation, *Private communication*.

- [9] Stothard, D.J.M., M.H. Dunn, and C.F. Rae, *Hyperspectral imaging of gases with a continuous-wave pump- enhanced optical parametric oscillator.* Optics Express, 2004. **12**(5): p. 947-955.

## Chapter Two – Data Acquisition and LCD Controller

(DALC) System

#### 2.1 Introduction

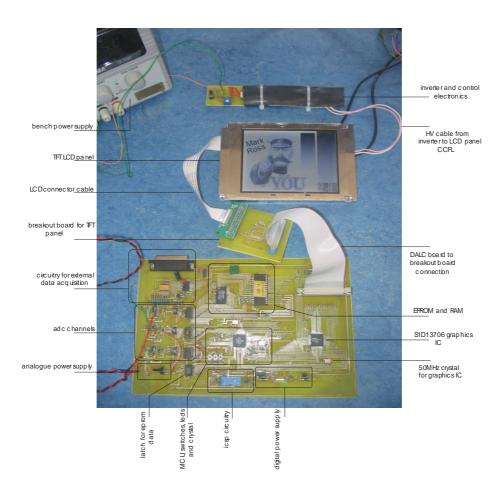

As outlined in the previous chapter, significant development work had already been invested in the development of the opto-mechanical polygonal hardware which makes up the scanning section of the BAGI device. In order to evaluate this hardware, an early supervisory electronic design was realised, in advance of the research programme outlined in this dissertation, which acquired pixel points and stored them in internal memory before uploading the data to a PC for viewing via custom-written software. This chapter outlines the early work undertaken in the course of this research in order to replace the existing electronic drive and host PC with a single device which integrates all of the scanning supervisory functions and high-resolution LCD display module and its associated drive electronics. Whilst the system described in this chapter had the capability of stand alone operation with control of the image acquisition hardware (polygon, galvanometer control and detector sampling as outlined in chapter 1) and display via the onboard LCD controller and high resolution display, we chose not to fully implement all of these features in this design. Instead, this early prototype was used to evaluate different options and technologies (for instance, the type of display technology used) for use in the finalised design as described in the following chapter. Therefore, the prototype design outlined in this chapter is more complex than the eventual final design necessitates. The opportunity for the evaluation of optimised track layout design for low noise analogue to digital conversion (ground starring, etc) was also undertaken in the device described in this chapter.

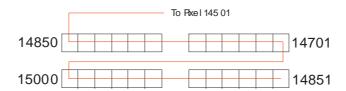

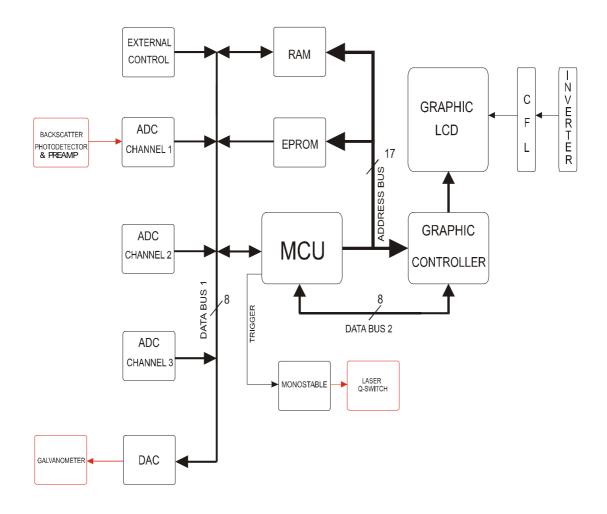

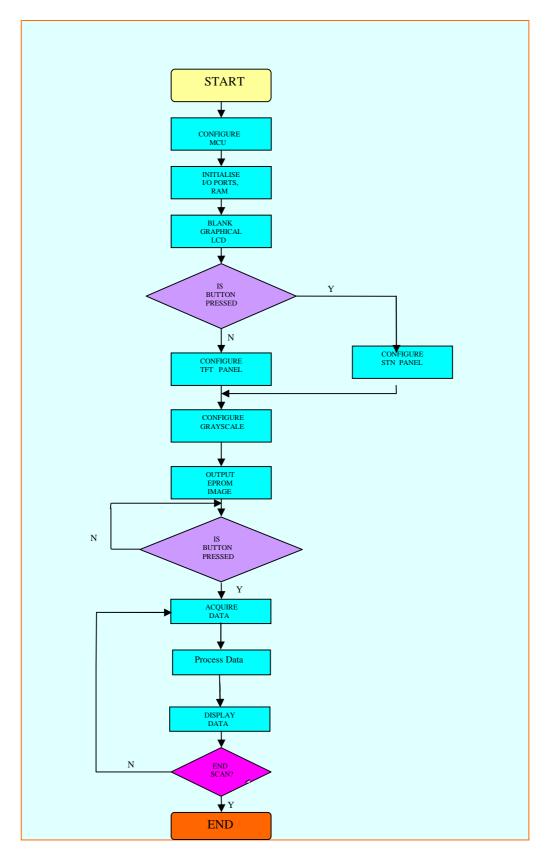

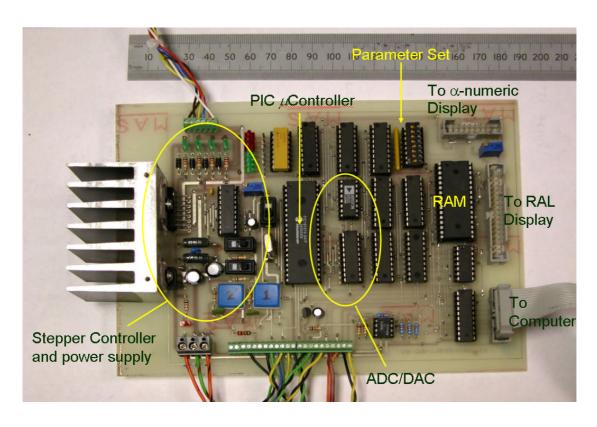

Instead of initially attempting to construct a stand alone module which both controls the optomechanical hardware of the scanner and the LCD display (which is the eventual desire), an interface was built in to the design which meant that the system could 'mimic' the operation of the host PC in the existing design and therefore interface to the existing image acquisition electronics. The two ways in which the design described in this chapter, the "Data Acquisition and LCD Controller" (DALC) system could be implemented is shown in figure 2.1 below.

Figure 2.1: Implementation of the DALC system, which can either connect to the opto-mechanical hardware directly, or via the existing control electronics by mimicking the host PC which is currently present.

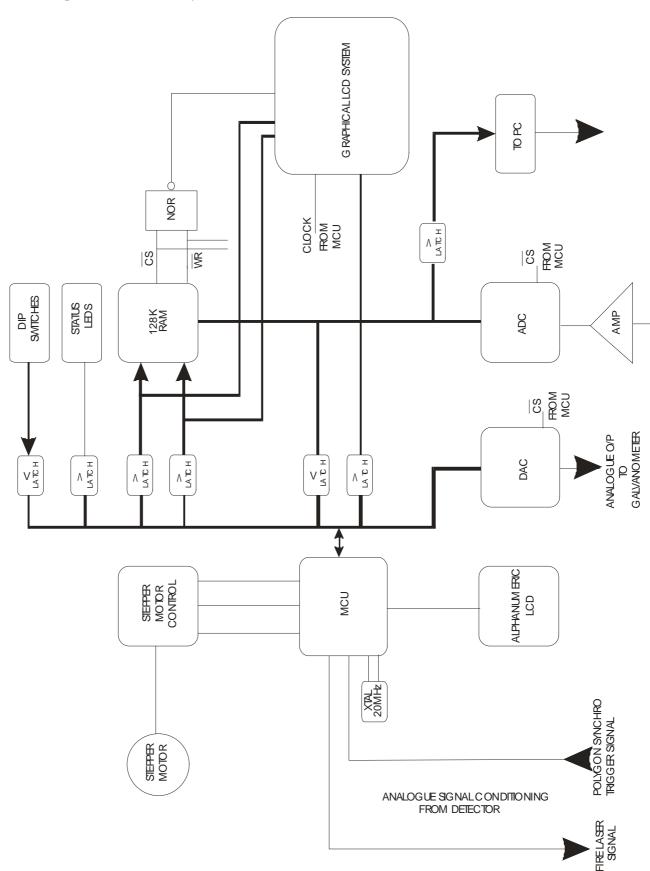

#### 2.2 Data Acquisition LCD Controller System

This section gives a brief overview of the key components of the Data Acquisition LCD Controller system (DALC). A more detailed description of the hardware follows in the next section. The DALC system can process data for imaging from either the external data acquisition system currently in use or directly from its own data acquisition/hardware control. This capability was incorporated into the design to maximise its flexibility, it also allowed the image display hardware (graphic controller, LCD panel) to be assessed without the need to implement those parts of the circuit dedicated to image data acquisition (ADC,DAC laser trigger in etc). Such a modular approach to testing allows the rapid diagnosis of design flaws present within the system. The pre-designed system utilises a PC for image display via custom written windows based software.

Figure 2.2: Block diagram of DALC system (external components shown in red).

#### 2.2.1Internal Data Acquisition

The hardware for the Internal Data Acquisition involves the ADC channels (for photodetector acquisition), the DAC (for galvanometer control), the RAM and the Monostable. These parts have been individually tested but have not yet been implemented as part of the Internal Data Acquisition, as the DALC system was superseded by a different design (chapter 3) before this became necessary.

#### 2.2.2 External Data Acquisition

The external data acquisition system is configured for images of 150 x 100 pixel resolution giving one frame a total of 15,000 pixels. The laser is capable of firing at frequencies of up to 350 kHz however

due to limitations in the scanning hardware the maximum scanning frequency the system can provide is 120 kHz. This means that the maximum frame the system can produce is 120000/15000 which equals 8 frames per second. The DALC system is designed with specifications of 10 frames per second with the possibility of potential scanning hardware improvements. Data transfer between the existing scan acquisition system and the MCU takes place of an 8-bit parallel interface and is controlled by two handshaking lines; one controlled by the MCU which tells the external system the MCU is ready to receive more data and one which is controlled by the external system tells the MCU it is ready send data. When data is received by the MCU it addresses the Graphic Controller and writes the data to the corresponding address via data bus 2, which in turn asynchronously updates the LCD panel. To obtain a 10 frames per second refresh rate with the image being 150x100 pixels, this process would be repeated in excess of 150,000 times per second meaning the MCU speed capability is a major factor (actual bandwidth requirements are, in practice, in excess of 15,000 due to the tone-burst nature with which the laser fires and the photodetector signal needs to be acquired).

The hardware parts required for external data acquisition in conjunction with the existing scan system are as follows:

| MCU   | The MCU controls and synchronises the whole DALC system which can be seen by the following descriptions. |

|-------|----------------------------------------------------------------------------------------------------------|

|       | system which can be seen by the following descriptions.                                                  |

| EPROM | The EPROM contains data from a greyscale bitmap to be                                                    |

|       | used at system start up in order to obtain best image quality                                            |

|       | before the external data acquisition images had been tested.                                             |

|       | The bitmap image is a resolution of 256 x 256 pixels. The                                                |

|       | LCD panels being used are of 320 x 240 resolution and so                                                 |

|       | the bottom 26 lines of the bitmap are not used.                                                          |

|       |                                                                                                          |

| RAM   | Multiple image data can be stored in the RAM. The future                                                 |

|       | requirements possibly being that two images of similar                                                   |

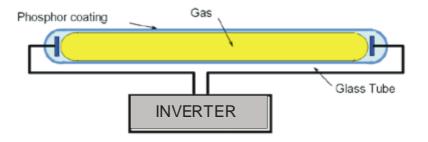

nature are stored and compared (differential imaging). The first image would be produced with the OPO being tuned at 3.31 microns and the other out with the methane absorption wavelength The second image would be subtracted from the first image leaving a third (differential) image being the methane. This methane image could then be modified in colour showing the intensity of the gas. This image could then be added to second image to show the background image in greyscale and the methane in a colour intensified image. This shows the need for the RAM to be capable of storing multiple image data. This process, however, requires improved design of the OPO in order for this to become possible and will be implemented in the future. The RAM can also be used in the internal data acquisition method. Graphic Controller The graphic controller reads data from its internal RAM and converts it into signals required by the LCD panel. These signals vary depending on the nature of the LCD panel being used. The controller has to be configured accordingly for different panels; this configuration being implemented by the MCU writing data to various registers. Most LCD panels are required to be refreshed at (approximately) 70Hz which the graphical controller handles independently thus freeing up software overheads of the MCU. Graphic LCD, CFL and The Graphic LCD panel produces the visual output for the Inverter DALC system. Most graphic LCD panels are transmissive meaning a panel backlight is required which is usually in

| the form of a cold cathode filament lamp (CCFL) with an |

|---------------------------------------------------------|

| inverter to drive the high voltage signal needed.       |

|                                                         |

|                                                         |

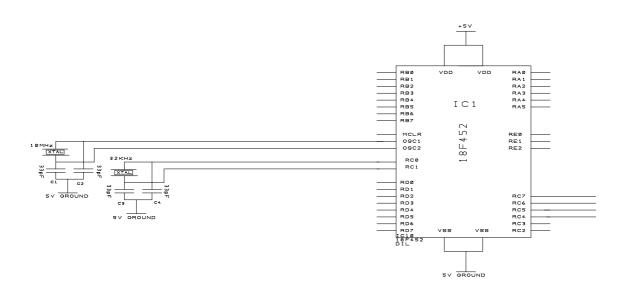

#### 2.3 Micro-controller Unit

The microcontroller unit used in the DALC system is the dsPIC30F6014 manufactured by Microchip Technology [3.1]. The device is a 16 bit high performance microcontroller capable of 30 million instructions per second (MIPS). It was chosen for the following reasons.

- Fast speed 30 Mips, sufficient for >10 frames per second refresh rate of the LCD panel.

- ➤ 16 bit data path allows for much quicker data transfer, processing and addressing within the system.

- > 144 kB on chip program memory space allowing for major future developments.

- 8 kB of on chip RAM which will become useful in future when OPO techniques allow for differential image manipulation when small sections of data can be transferred into and out of this useful memory allocation.

- Easy programming via in circuit serial programming (ICSP).

- ▶ 84 user-selectable I/O pins allowing for freedom in design methods.

- Low cost in comparison to competitive MCU's.

- Future pin for pin compatible upgrades will become available with easy integration into current design.

- Easy code migration from previous microchip MCU's which previous experience and familiarity allows for quicker development.

#### 2.3.1 Micro-Controller Unit Configuration

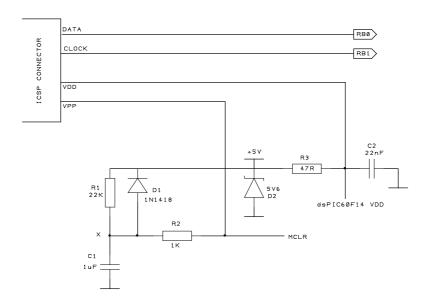

The dsPIC30F6014 requires a clock source which dictates the speed at which each instruction is executed. The MCU clock is configurable in a variety of ways and can easily be switched between different sources in software. The 10 frame per second refresh rate requires fast instruction execution

times to acquire data of 15,000 pixels per frame (at a resolution of 150x100 pixels). The source chosen for MCU clock is a 6 MHz crystal module and is programmed in such a way that this frequency is multiplied by 16 via an internal phase-locked loop to give an operating frequency of 96 MHz which is subsequently divided by 4 to allow the device to run at 24 Mips, yielding single instruction execution time of 42 ns. Fast clock sources require special RF considerations. For example, a 48MHz external clock could be multiplied by 2 internally by the on chip PLL to give the same results. The problem with this approach is that more careful considerations for RF and board layout are required to accommodate such a high frequency clock. So the best solution is to use a combination of a low external clock source and a high PLL multiple to achieve the desired result. The maximum PLL multiple on the device is x16. Although the MCU internal frequency runs at 96MHz it is designed with these considerations in mind to have little effect externally.

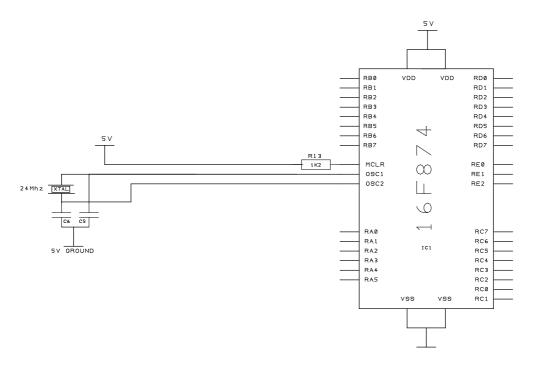

Figure 2.3: MCU reset and ICSP schematic [2].

Figure 2.3 shows the reset pin and In Circuit Serial Programming (ICSP) circuit implemented in the system. The ICSP becomes necessary because the MCU is a surface mount device which is soldered directly into the system board and therefore is programmed in circuit as opposed to being removed from the circuit and being inserted into a programming device. The two programming lines CLK and

DATA are isolated from the system by the means of two 10 K $\Omega$  resistors. VDD has a decoupling capacitor to ground and the zener diode gives protection from spurious signals by clamping them at 5.6 V. R1 and C1 form the RC reset network to the MCLR pin with D1 giving protection at point x should it rise 0.6 V above the 5 V supply. Figure 2.3 shows how this circuitry was integrated into the system.

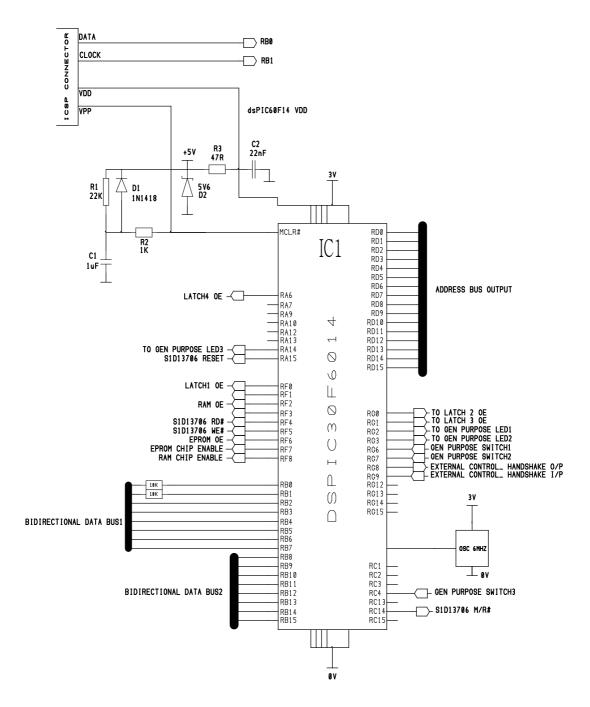

The dsPIC30F6014 has 84 easily configurable I/O pins arranged in various bit widths in the format of PORTA-PORTG. The I/O pins can have multiple functions, e.g. can be used for A/D input, PWM output, etc. This application of the MCU requires that all I/O used should be configured for straightforward digital I/O. Figure 2.4 shows how the I/O pins were configured for use within the system. The two sixteen bit ports available were selected for both 8 bit data busses and the 16 bit address bus. This was to speed up data transfer and addressing. The remaining allocation of the I/O pins were chosen with PCB design in mind allowing for shorter tracks and simplicity of board layout.

#### 2.4 Graphic Controller

Very early on in the project it became apparent that direct control of the LCD display by the microprocessor would require a huge overhead in processing power, and would therefore not be practical. This is due to the non-static nature of the LCD module which continually needs to have each pixel point "refreshed", regardless of if a change at a particular pixel point is required – somewhat analogous to dynamic memory. A dedicated LCD matrix controller was therefore procured which would enable much simplified interfacing of the microcontroller to the LCD display. The chosen device used for graphic control in the system was the S1D13706 manufactured by Epson research and development [3]. The main attraction to the device is its ability to produce 64 shades of grey on various panel types i.e. STN, TFT, D-TFT and HR-TFT. It's on chip 80 Kbytes of video random access memory (RAM) make it adequate as a maximum of 76 Kbyte of RAM is required for the 320x240 panels used. The S1D13706 requires hardware and software configuration in order for it to be used successfully in the system. This section will cover hardware configuration and how the graphic controller was implemented into this system.

Figure 2.4: MCU clock circuit, Pin I/O configuration and ICSP/Reset circuitry

#### 2.4.1 S1D13706 Bus Configuration

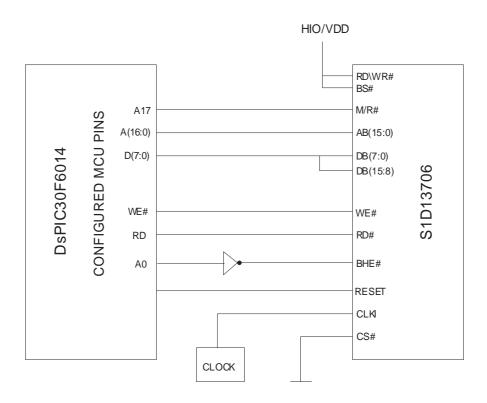

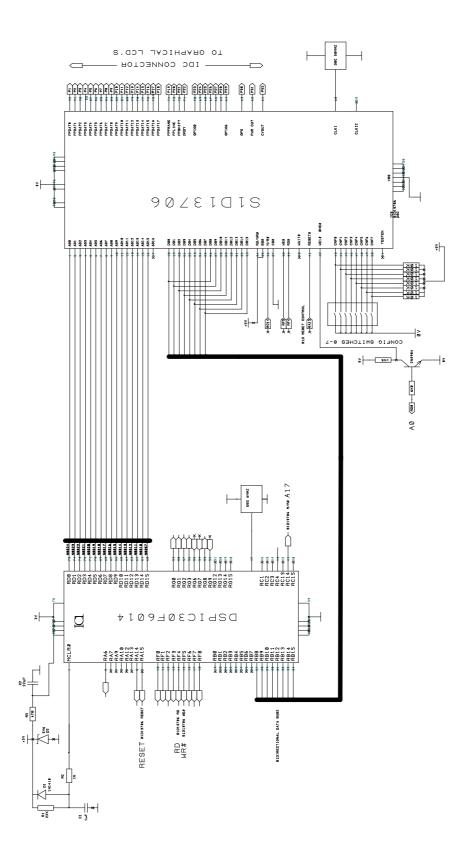

The device can be used with a host of microprocessors or microcontrollers and is engineered for ease of use with fast, powerful devices such as Motorola 32-bit 68030, Motorola 16-bit 68000, Motorola Dragonball, Hitachi SH3 and SH4 and many others. These devices are optimised for use in more demanding applications and can be embedded into single board computers. The device can also be

configured for generic bus interfacing to a microcontroller which is the method used within this system, in either 8 or 16 bit data transfer mode. The configuration chosen was 8 bit data transfer. Addressing of the graphic controller was configured by means of a 17 bit data interface to the MCU. The generic bus used is shown in figure 2.5. Bus start (BS#) and Read/Write (RD/WR#) are not used in the generic interface bus mapping and are tied to HIO/VDD. The memory mapping of the device is separated into two 128 Kbyte blocks, one of which is occupied by the internal registers and the other block is occupied by the 80 Kbyte display buffer. Pulsing M/R# high selects the display buffer memory and a low selects the register memory. Address bus 16:0 allows addressing to each of the 128 Kbyte of memory with the least significant bit of the bus selecting either the low byte or high byte of data, A0 low onto BHE# enables the high byte and a logic high enables the low byte. This is how 8 bit interfacing becomes possible. The RD# and WR# pins instruct whether data is read from the device or written to it. Reset to the graphic controller is controlled by an I/O pin enabling a software controlled reset.

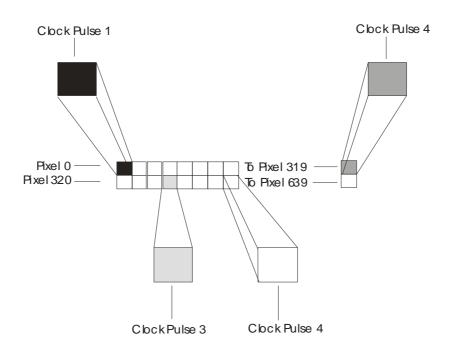

#### 2.4.2 S1D13706 Clock Configuration

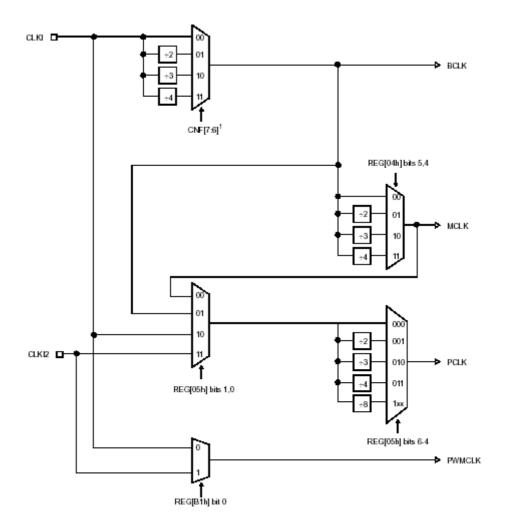

The clock source used for the S1D13706 is a 50 MHz signal to the device is a crystal module that requires a 3 V supply across it. The device can be driven by one clock source as in this system or 2 clock sources. If two clock sources are used then the second clock source drives the output signals for the LCD panel directly and is optimised to derive the required frame rate for the panel – this source is the pixel clock (PCLK). The device has 4 internal clocks, bus clock (BCLK), memory clock (MCLK), pixel clock (PCLK) and pulse width modulation clock (PWMCLK) which can be used to output a PWM signal for backlight brightness control but is not required in this system as the inverter in this system has independent control. In this system BLCK, MCLK and PCLK were all derived from the CLKI source. The clock frequencies are all software configurable and were set as CLCKI = BCLK = MCLK = 50 MHz. PCLK=CLKI/8 = 6.25 MHz. Figure 2.6 shows the logical representation of the internal clocks and the registers required to modify them.

Figure 2.5: Block diagram of dsPIC30F6014 and S1D13706 interface

#### 2.4.3 S1D13706 Configuration Options

The S1D13706 has "power on" hardware configuration options which are shown in figure 2.7. The options available are selectable by 8 pins (CNF0-CNF7) set by external logic. The configuration required by the system are as follows.

- ➤ Generic #2, Little endian

- CNF3 doesn't matter. No output pins used.

- ➤ CNF5 doesn't matter, wait state not required. Only required when MCU/MPU read write times < 5 ns as not to cause bus collision. The system MCU instruction cycle time is 42 ns.

- ➤ CLK1 to BCLK divide ratio 1:1 making BCLK 50MHz.

The logic levels are selected via PCB mounted configuration switches being connected to 0 V or Vdd. Little Endian and Big Endian refers to the way data is transmitted on a data bus. If 16 bit data had a value of 0xFEDC (hex) it would appear on the data bus as msb - FEDC - lsb. Big endian would appear as follows, msb - DCFE – lsb. i.e. it swaps the bytes. This option is available because some MCU's or MPU's have different endian states.

Figure 2.6: Logical representation of the S1D13706 internal clocks

| S1D13706               | Power-On/Reset State                         |                |                |                |                                                                                       |  |  |

|------------------------|----------------------------------------------|----------------|----------------|----------------|---------------------------------------------------------------------------------------|--|--|

| Configuration<br>Input | 1 (connected to NIOV <sub>DD</sub> )         |                |                |                | 0 (Connected to V <sub>SS</sub> )                                                     |  |  |

|                        | Select host bus into                         | erface as      | follows:       |                |                                                                                       |  |  |

|                        | CNF4<br>1<br>0                               | CNF2<br>0<br>0 | CNF1<br>0<br>0 | CNF0<br>0<br>0 | Host Bus<br>SH-4/SH-3 interface, Big Endian<br>SH-4/SH-3 interface, Little Endian     |  |  |

|                        | 1                                            | 0              | 0              | 1              | MC68K #1, Big Endian                                                                  |  |  |

|                        | 0<br>1                                       | 0              | 0<br>1         | 1<br>0         | Reserved<br>MC68K #2, Big Endian                                                      |  |  |

|                        | 0                                            | 0              | 1              | 0              | Reserved                                                                              |  |  |

| CNF4,CNF[2:0]          | 1                                            | 0              | 1              | 1              | Generic #1, Big Endian<br>Generic #1, Little Endian                                   |  |  |

| CNF4,CNF[2.0]          | 1                                            | 1              | ò              | ò              | Reserved                                                                              |  |  |

|                        | Ö                                            | 1              | ō              | ō              | Generic #2, Little Endian                                                             |  |  |

|                        | 1                                            | 1              | 0              | 1              | REDCAP2, Big Endian                                                                   |  |  |

|                        | 0                                            | 1              | 0              | 1              | Reserved                                                                              |  |  |

|                        | 1 0                                          | 1              | 1              | 0              | DragonBall (MC68EZ328/MC68VZ328), Big Endian<br>Reserved                              |  |  |

|                        | x                                            | 1              | 1              | 1              | Reserved                                                                              |  |  |

|                        | Note: The host bus interface is 16-bit only. |                |                |                |                                                                                       |  |  |

| CNF3                   | Configure GPIO pins as inputs at power-on    |                |                |                | Configure GPIO pins as outputs at power-on (for use<br>by HR-TFT/D-TFD when selected) |  |  |

| CNF5                   | WAIT# is active high                         |                |                |                | WAIT# is active low                                                                   |  |  |

| CNF[7:6]               | CLKI to BCLK divide select:                  |                |                |                | •                                                                                     |  |  |

|                        | CNF7<br>0<br>0                               | CNF6<br>0<br>1 |                |                | CLKI to BCLK Divide Ratio<br>1:1<br>2:1                                               |  |  |

|                        | 1                                            | 0              |                |                | 3:1                                                                                   |  |  |

|                        | 1                                            | 1              |                |                | 4:1                                                                                   |  |  |

Figure 2.7: Power on reset options [3]

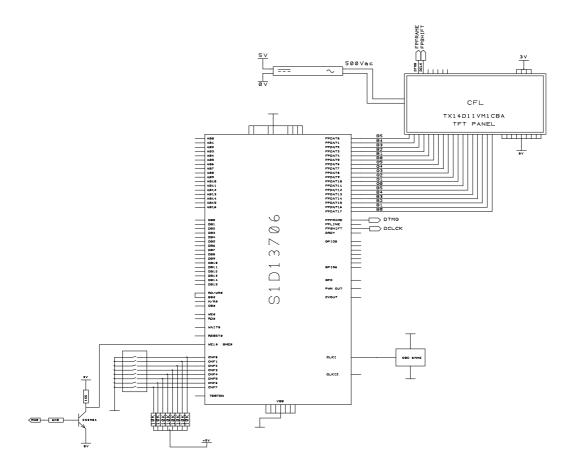

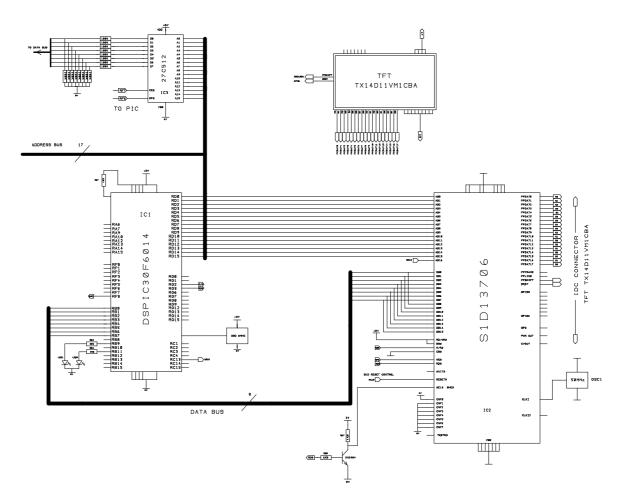

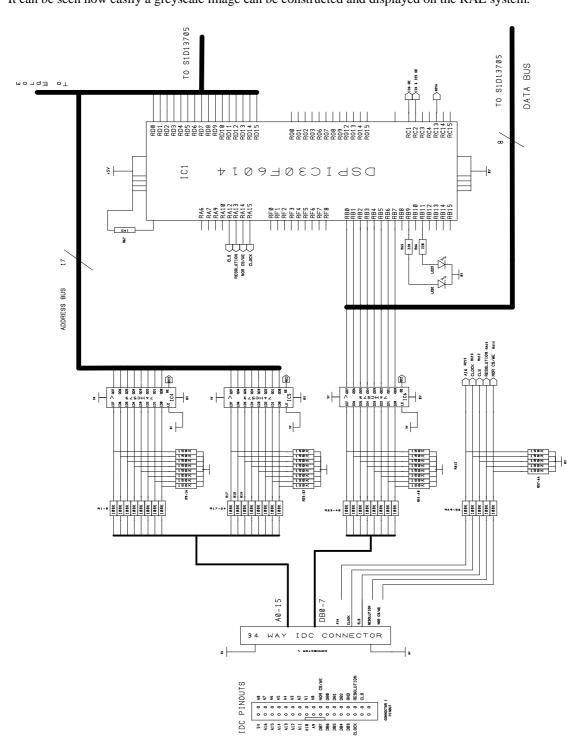

Figure 2.8 shows the schematic of how the hardware of the S1D13706 was configured and the manner in which the S1D13706 was interfaced to the dsPIC30F6014. The outputs from the S1D13706 go to the LCD panel. The outputs in this system were connected to an IDC plug so any panel that the S1D13706 could drive could be connected to the system via a specific interface board designed for that panel.

### 2.4.4 Refresh rate calculation

Refresh rate of the LCD screen is calculated by the following formula where RR is the refresh rate, fPCLK is the pixel clock frequency, htotal is the horizontal total of the LCD panel and vtotal is the vertical total of the LCD panel.

$$RR = \frac{fPCLK}{htotal*vtotal} = \frac{6.25MHz}{320*240} = 81.4Hz$$

Figure 2.8: S1D13706 hardware and MCU interface schematic

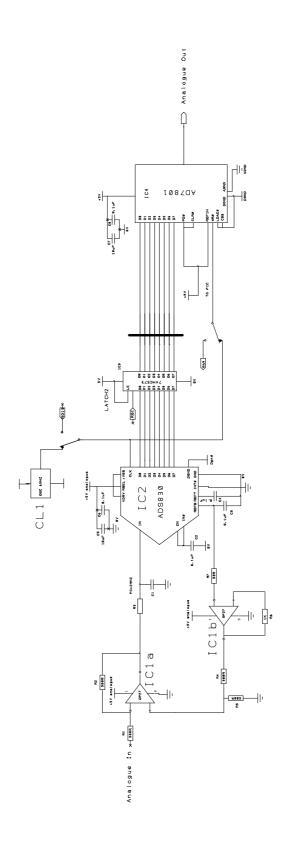

# 2.5 Analogue to Digital Converter Channels

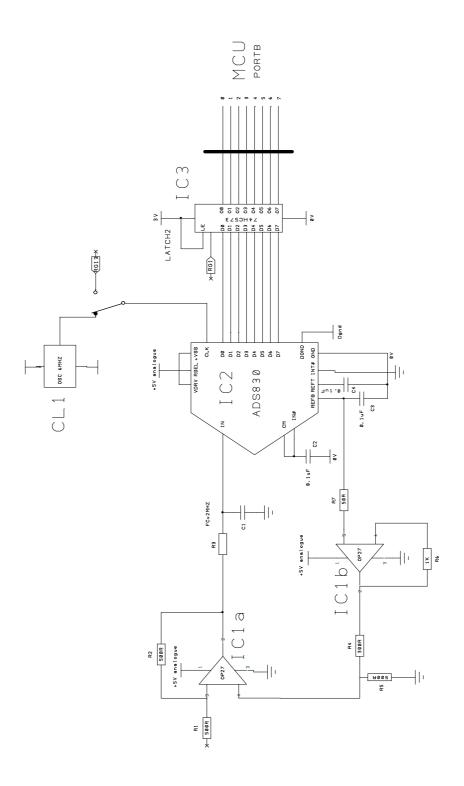

The ADCs integrated within the microcontroller was not used as its maximum sampling frequency was inadequate for this application. Instead, three identical discreet analogue to digital converters with their own pre-amplification were used. They are based around the 8-bit analogue to digital converter ADS830 [6]. The device was chosen because of its high bandwidth capability, low distortion and high SNR ratio making it ideal for high bandwidth, low noise applications such as this. The device is capable of a 60 MHz sampling rate; significantly greater than the required 200 kHz required for a 10 frames per second refresh rate. However, possible future requirements make a higher bandwidth desirable. For example, one way to greatly reduce noise is to take a number of samples and then average the total and hence average out the noise. If 20 samples were taken the required bandwidth increases to 4 MHz, this could double should a 20 frame per second refresh rate be required and increase yet again if resolution was improved. This could therefore be implemented with ease into future designs.

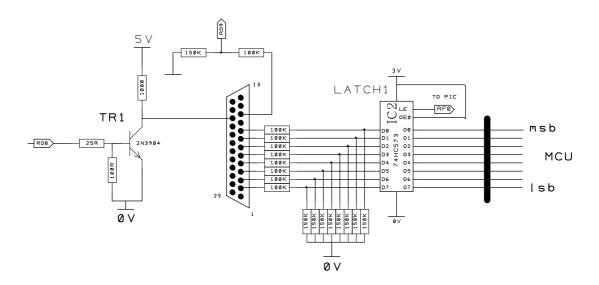

The A/D requires voltage levels to be at a certain level and this biasing was achieved by the inclusion of an operational amplifier. The operational amplifier used in this design is an OPA2681 [7] which was chosen because of its high bandwidth – 150 MHz at 1-4 volts output swing and low noise low distortion capabilities. The OPA2681 is a dual current feed back device which enables the high bandwidth required. One op amp – IC1a drives the input of the ADS830 and the other – IC10b level shifts the signal to be compatible with the A/D input range. The RSEL pin is tied to +5V which allows a 2 Vp-p input range to the channel and the INT/EXT pin is tied to ground which means the device is using the internal reference (2 V). IC10b buffers the REFB pin from the potential divider R4 and R5 to give 1.25 V into the non inverting pin of IC1a giving the correct DC level of 2.5 V for the signal input (IN). The pins CM, IN, REFB and REFT are all bypassed with 0.1μF capacitors. It is important to note that everything described so far is connected to the analogue supplies with the ADS830 being treated as an analogue device. The voltage at the input (IN) will be converted and placed on the 8 bit data bus on every rising edge of the input clock which is selectable between OSC1 or RG13 of the MCU. This option is to free up software overheads by using OSC1 if required. The data is not transferred onto the main data bus until the output enable pin of IC3 is pulled low. The output of IC3 remains in a high

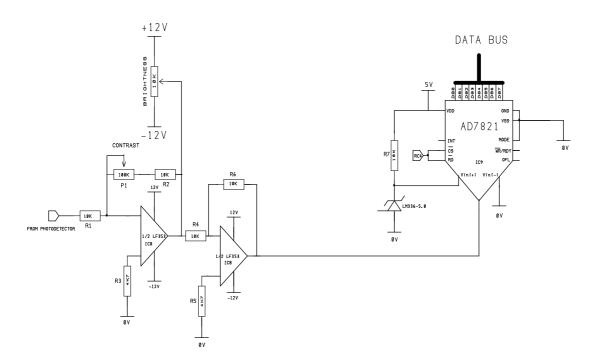

impedance state whilst the output enable pin is high allowing other devices command of the bus. When the data is on the main bus it allows the MCU to register the data via PORTB bits 0-7. Figure 2.8 shows the schematic of one of the A/D channels.

Figure 2.8: A/D channel schematic with latch

### 2.5.1 Separating Analogue and Digital Grounds for Noise Reduction.

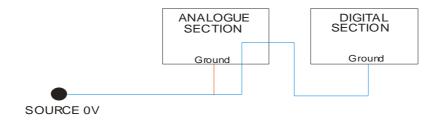

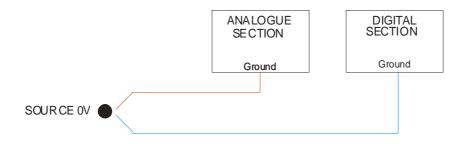

It is vital when measuring precise analogue data in mixed systems that ground paths have to be laid out carefully. This is because digital circuits generate a 'noisy ground' and this can lead to huge errors if this 'noisy ground' is the reference when acquiring sensitive analogue data. The solution is to separate analogue and digital ground paths and join them at a common point usually at the ground point of the power source (a technique known as starring). The ADS830 is treated as an analogue device with the digital part (the clock input and the data outputs) having its own ground for a separate return path so not to inject noise into the analogue part of the IC.

(a)

(b)

Figure 2.9: Grounding options in a mixed signal system (a) Incorrect (b) Correct

Figure 2.9 (a) shows the incorrect method of grounding mixed signal circuits. The blue digital ground path passes directly through the red analogue ground path which therefore forces the analogue ground path to be of poor quality and hence analogue signals being converted will have a high proportion of error due to the digital noise. Figure 2.9 (b) shows the correct method. Both sections have their own return path to the source 0V so the analogue ground is isolated from noise generated by the digital ground.

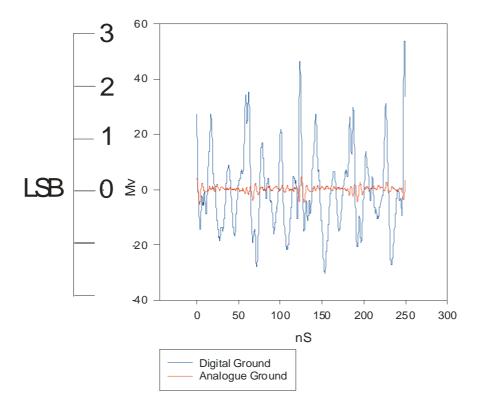

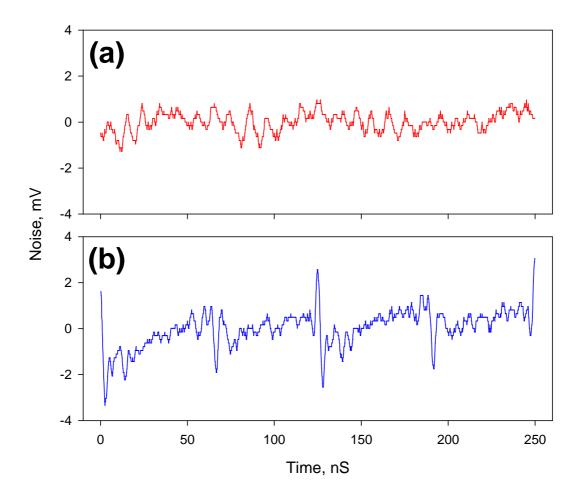

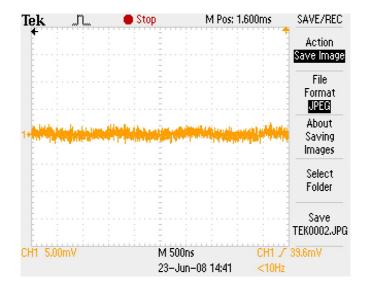

Figure 2.10: A comparison of noise present in the digital and analogue grounds.

The two traces from Figure 2.10. are measured from the two 'separated grounds' on the system. It can be seen that the analogue ground is of a much better quality than that of the digital ground. However if the ground paths were connected as in diagram 2.9 (a) then both grounds would be of similar magnitude i.e. Digital ground. The analogue ground has a magnitude of approximately 8 mV p-p whereas the digital ground has a magnitude of approximately 90 mV p-p thus minimising any errors whilst sampling the analogue signal. This low level noise ensures no least significant bit (LSB) errors occur whereas at 90 mV the resultant error could be as much as 4 LSB's making measurements very inaccurate.

# 2.6 Digital to Analogue Converter

The digital to analogue converter (DAC) used in the system (included to provide the analogue positional drive signal for the galvanometer) is an 8-bit AD7801 from Analog Devices [8]. The data appearing from the bus appears on the high speed parallel input of the D/A. The device is configured in such a manner that it is updated on the rising edge of WR. This is done by permanently tying the LDAC pin low. The reference of the device is generated internally and is configured by tying the reference pin permanently high. By selecting the internal reference the output of the device is Vdd/2. The clock into the WR# pin is again selectable between OSC1 and RA9 to allow for the possibility of reducing software overheads if required. The DAC output was tested by applying a 1.5 Vp-p AC signal into an ADC channel, with the latch output enable pulled low to allow the converted data to appear on the bus. This data therefore appears at the DAC high speed parallel input. Both the ADC and DAC are driven by Clock 1. On every rising edge of Clock 1 data is converted to its analogue output. Figure 2.12 highlights the distortion between the input analogue signal and the output analogue signal. The output signal is still of acceptable magnitude being only 4mV p-p which is well within the least significant bit error of 19 mV. Better considerations to ground layout and increasing track thicknesses for the supply lines (to reduce inductance) should suppress these peaks further. Figure 2.11 shows the schematic of how the D/A converter was integrated into the system and tested with an A/D channel.

### **2.7 EPROM**

The EPROM used for the static image "test screen" was a 27C512 [9]. It was chosen because of its ease of programming and its ability to store 64KByte of data. This allowed for the bitmap image of 256x256 to be stored on the IC (256x240 displayed on panel). Once programmed the device is easily controlled by enabling the OE# making the data outputs high impedance state to free up the bus or by disabling the pin for the data to take command of bus. Another control input to the device is the CE# which when enabled switches the device to a low power standby mode. Both these lines are controlled by the MCU. The EPROM shares the sixteen LSB's of the address bus and when the two control lines are disabled the data stored on the corresponding address appears on data bus 1. Figure 2.13 shows the

Figure 2.11 : D/A schematic and system integration

# Signal Distortion

Figure 2.12: Distortion of signal (a) before and (b) after being processed via A/D then D/A

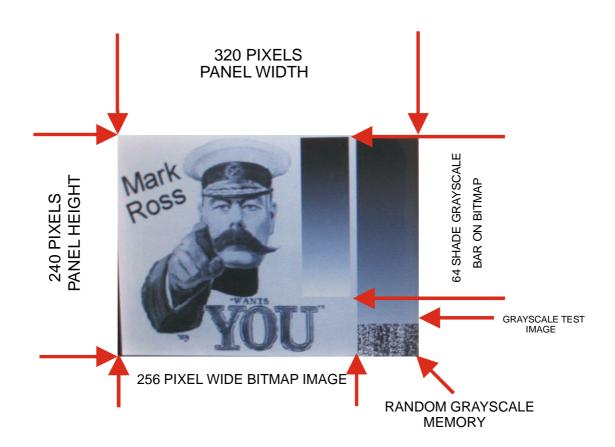

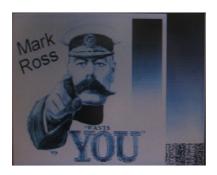

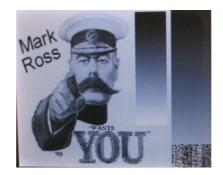

256 greyscale PC bitmap image that was programmed onto the EPROM. The image of General Kitchener, an instantly recognisable black and white image, was chosen specifically to highlight the greyscale quality of the black and white display and also its high resolution. The 256 shade greyscale bars highlight this with the gradual blending from black to white. This image, stored at a bit depth of 8-bits (i.e. 256 shades of grey) will be rendered on the screen in 64 shades of grey due to the limitations of the LCD module and the graphics IC. Reduced bit depth can lead to "postarisation" where smooth gradients are quantised into blocks of tone and the grey graduate strips were included in the image to facilitate evaluation of this effect in the use of these displays. The limitation of 64 shades of grey comes about due to the intensity resolution of the RGB components within the display module. Each red, green and blue pixel point has only 6-bit (i.e. 64 level) intensity resolution. When used as a colour

display, this yields a palate of 18 bits (262144 different colours), but when used as a black and white display (when R=G=B) this falls again to only 6-bit intensity resolution, hence 64 shades of grey.

Figure 2.13: 256 greyscale test bitmap image

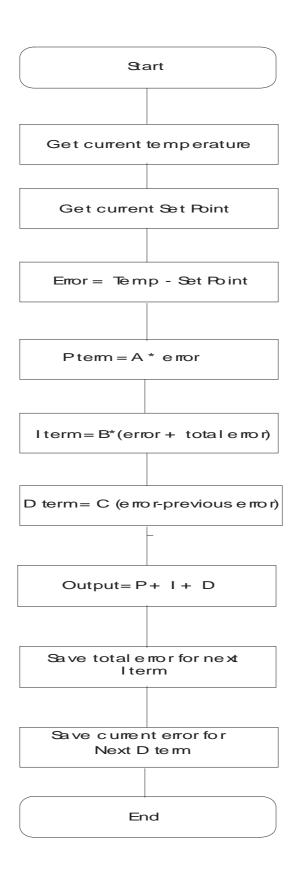

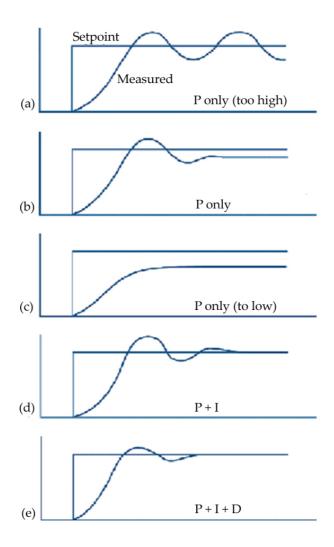

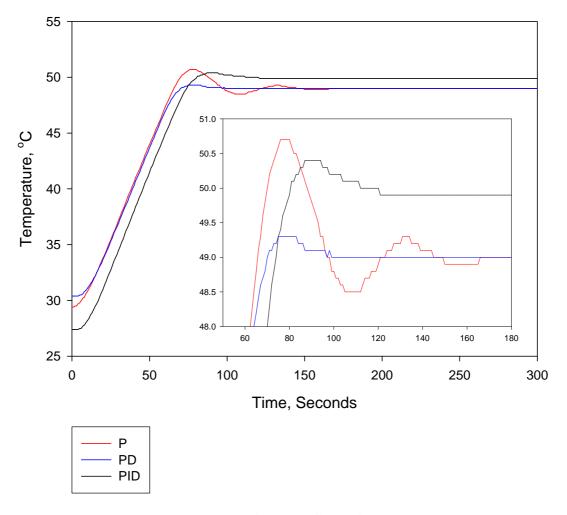

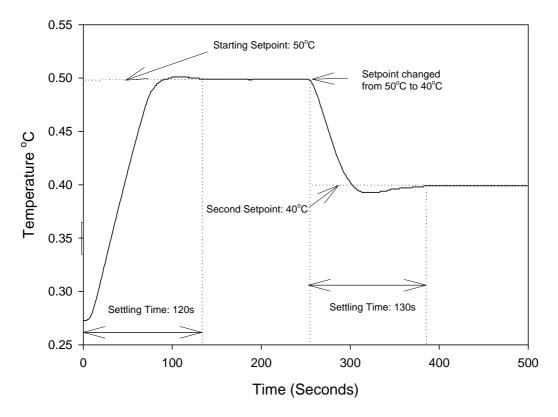

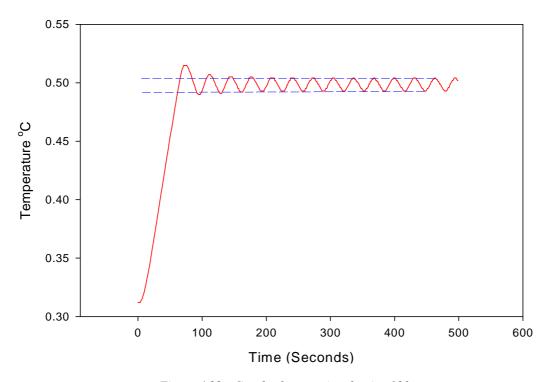

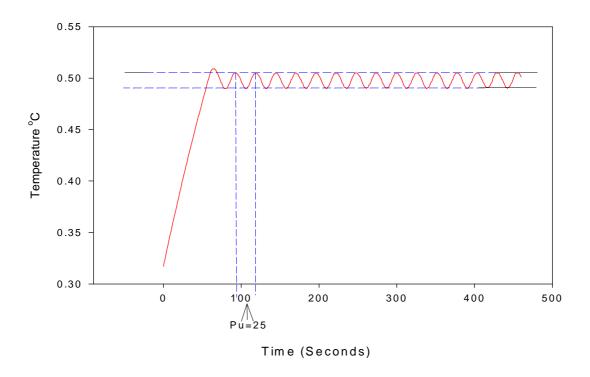

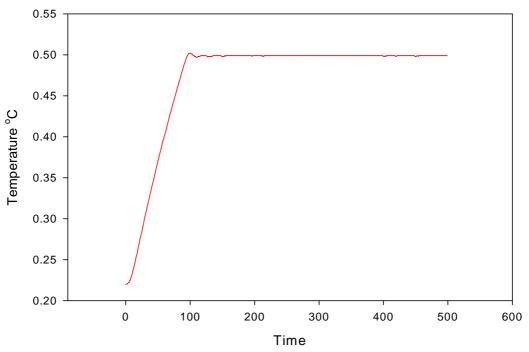

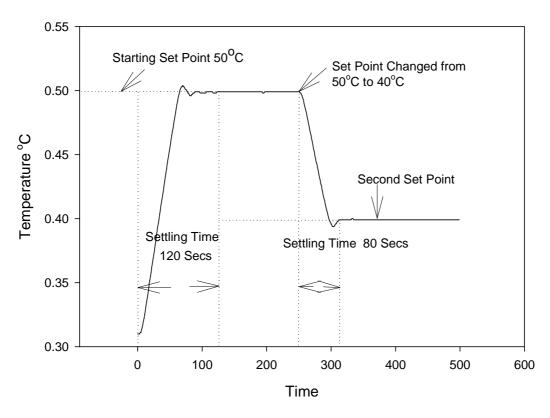

### 2.8 Random Access Memory